计算机组成原理笔记

计算机组成原理笔记

# 计算机组成原理笔记

# 存储器

现代计算机以存储器为中心,它是计算机中存放指令和数据的主要部件

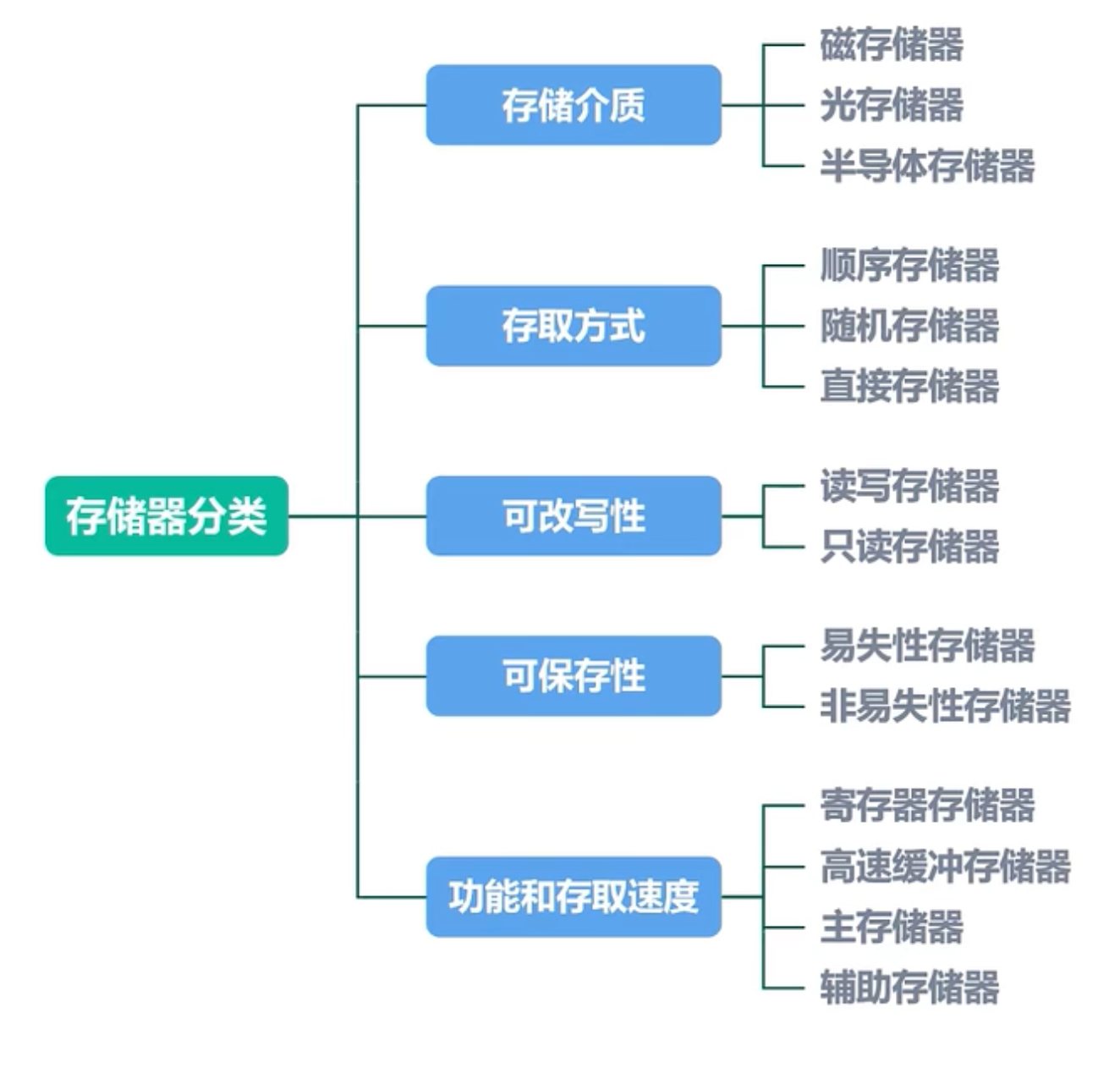

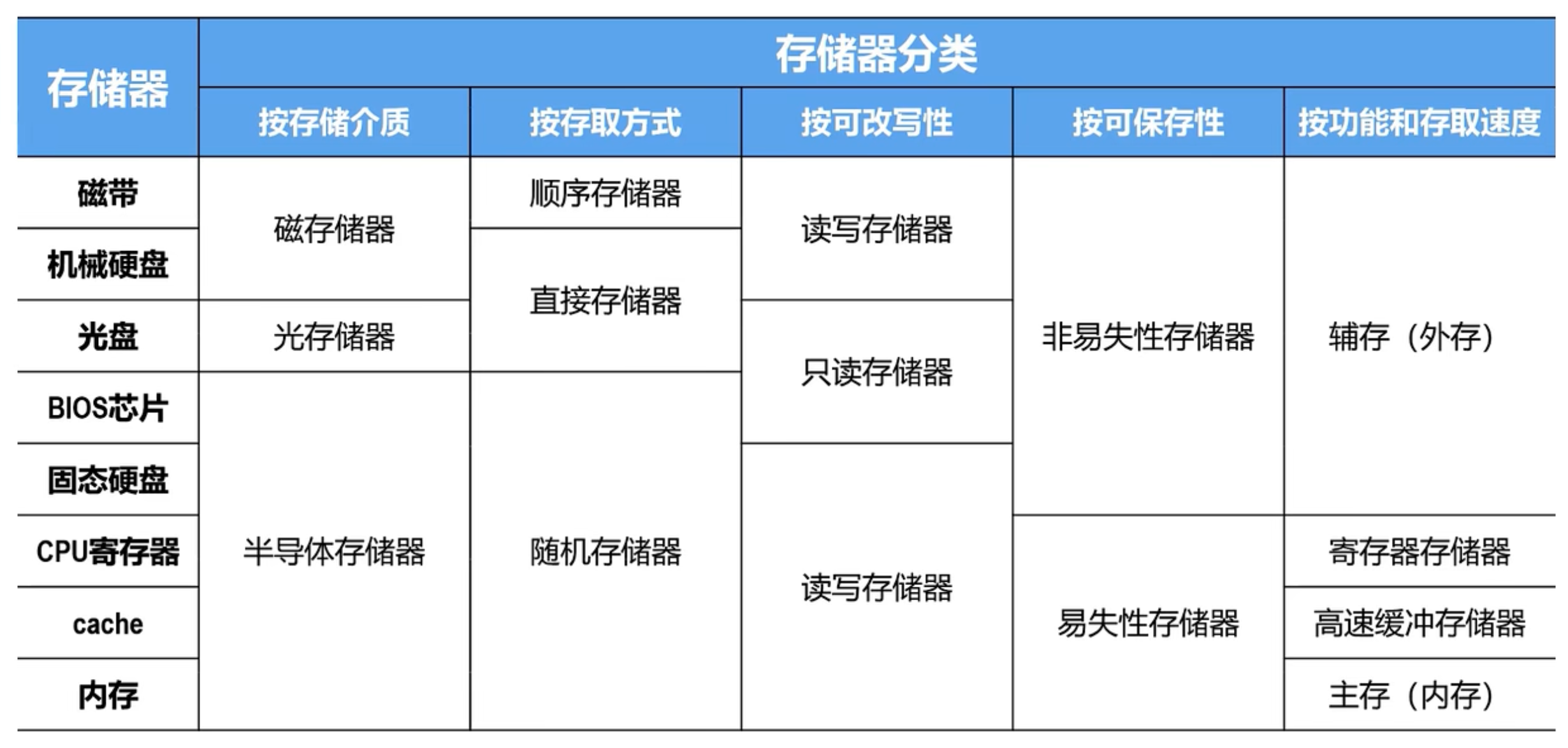

# 存储器分类

# 存储器性能指标

- 存储容量:可以存储的二进制信息的总量

存储容量 存储字长 存储单元数量

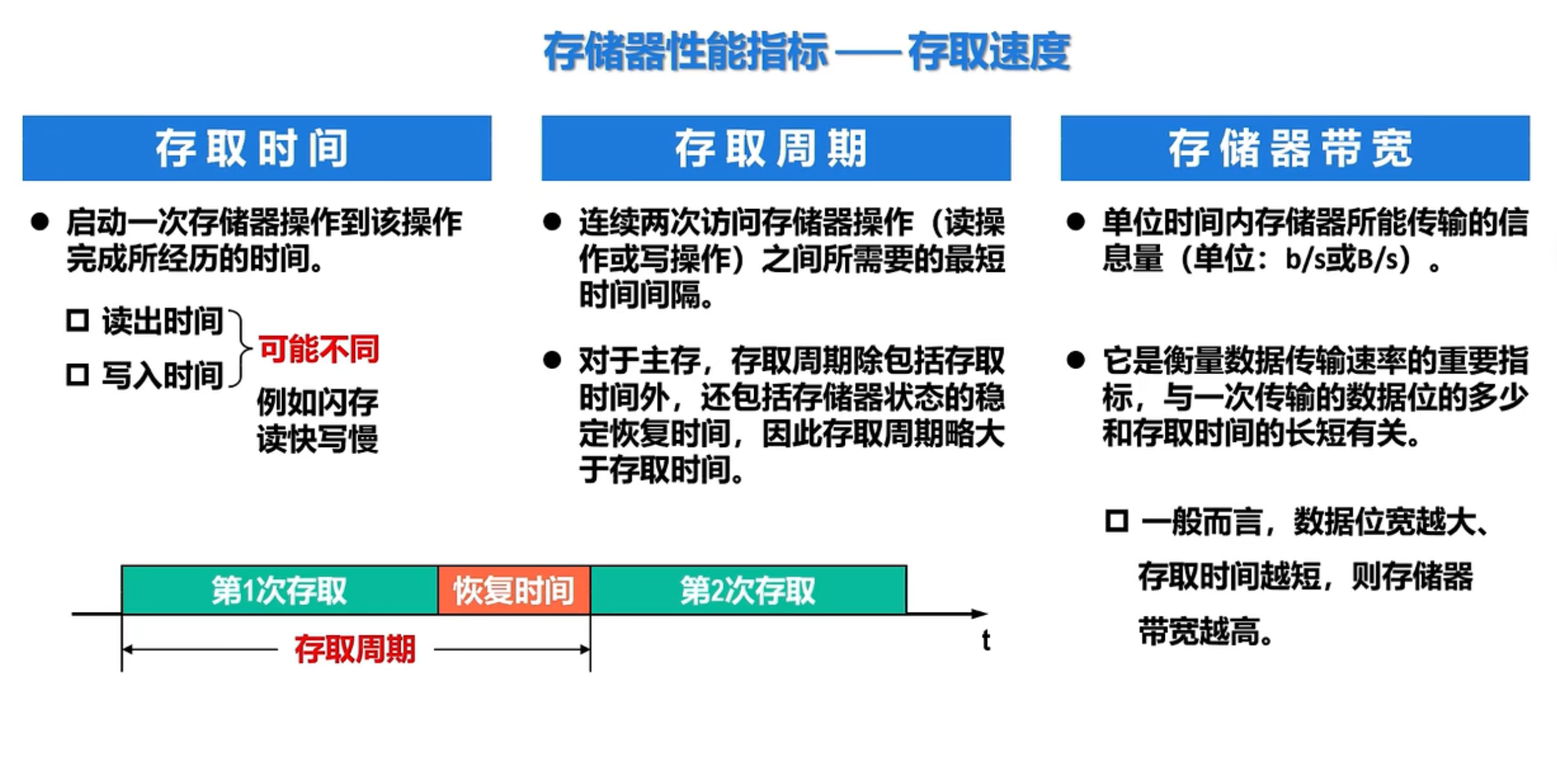

- 存取速度,分为三个部分

- 存取时间

- 存取周期

- 存储器带宽

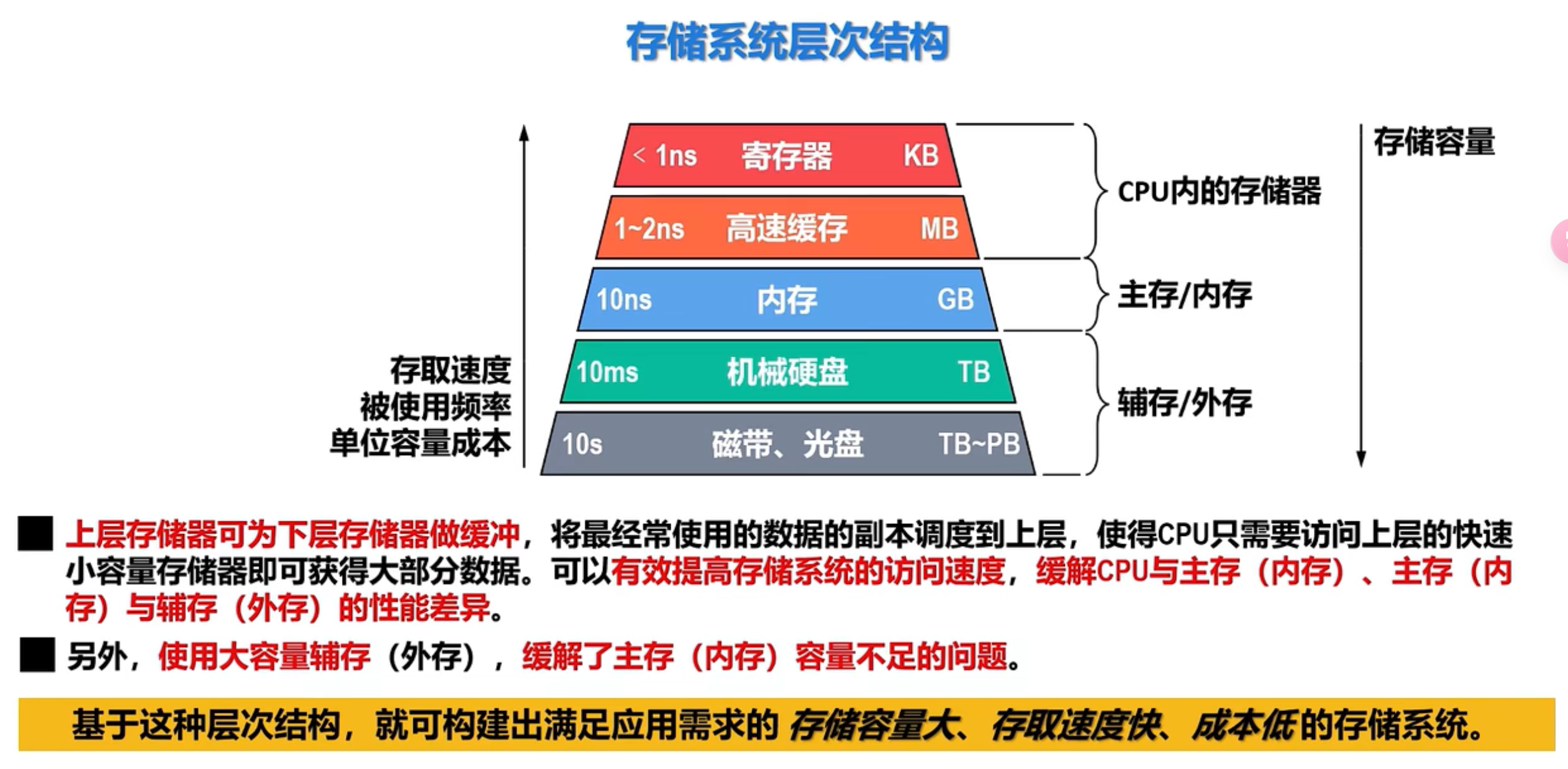

# 存储系统层次结构

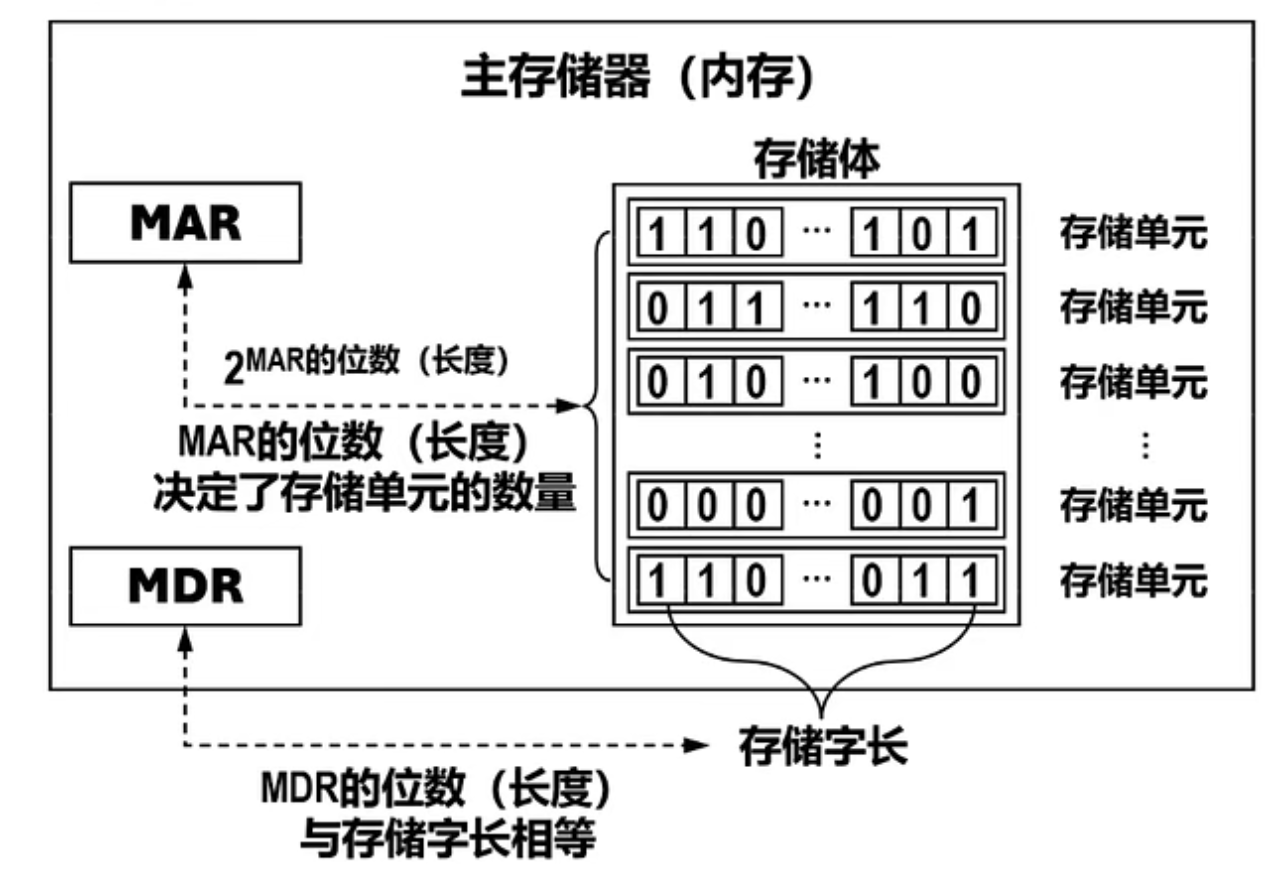

# 主存储器

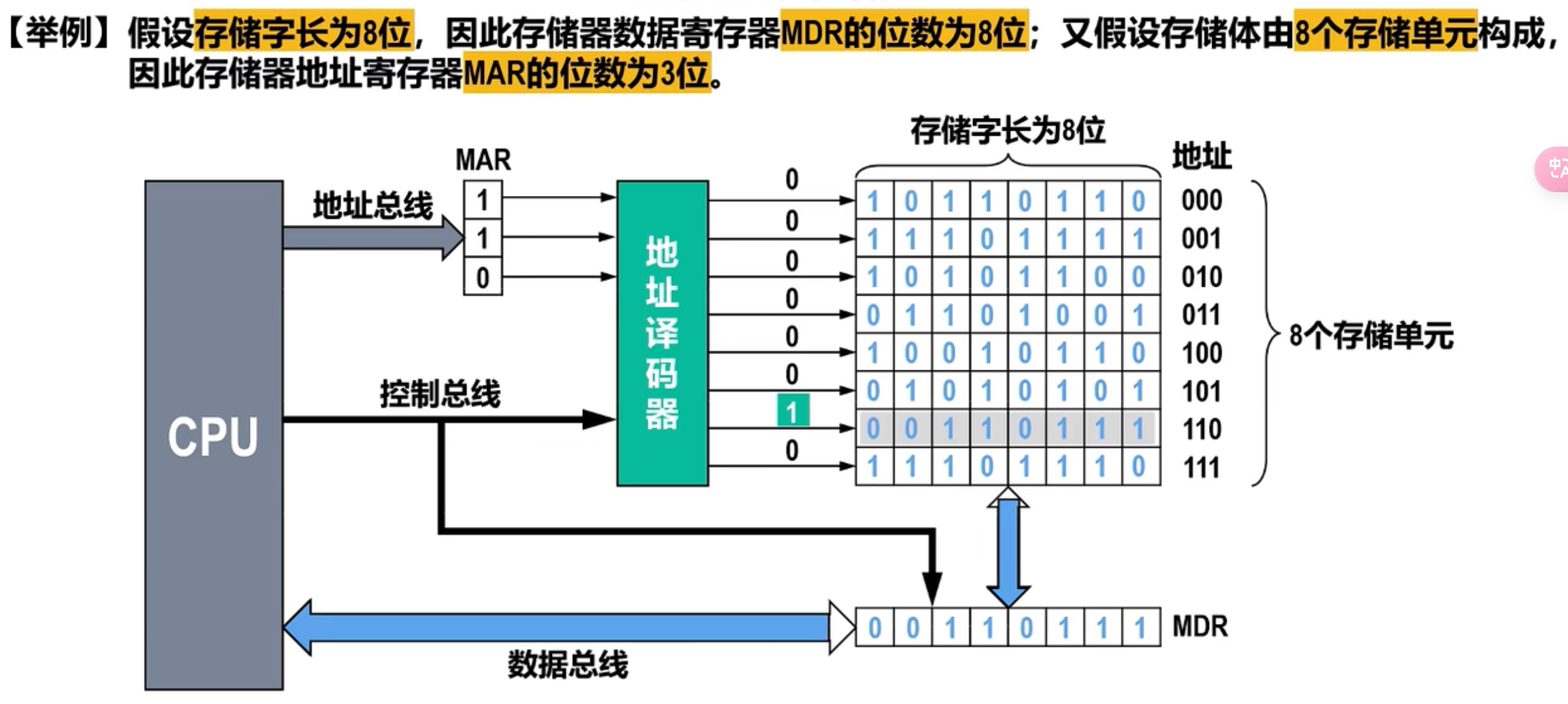

读入信息的过程,假设要读取 110 位置的信息

- 首先 CPU 通过地址总线把 110 给 MAR

- MAR 把 110 传给译码器,译码器选中第 6 个位置

- 存储器复制第 6 个位置的字节到 MDR 中

- MDR 通过地址总线把数据传给 CPU

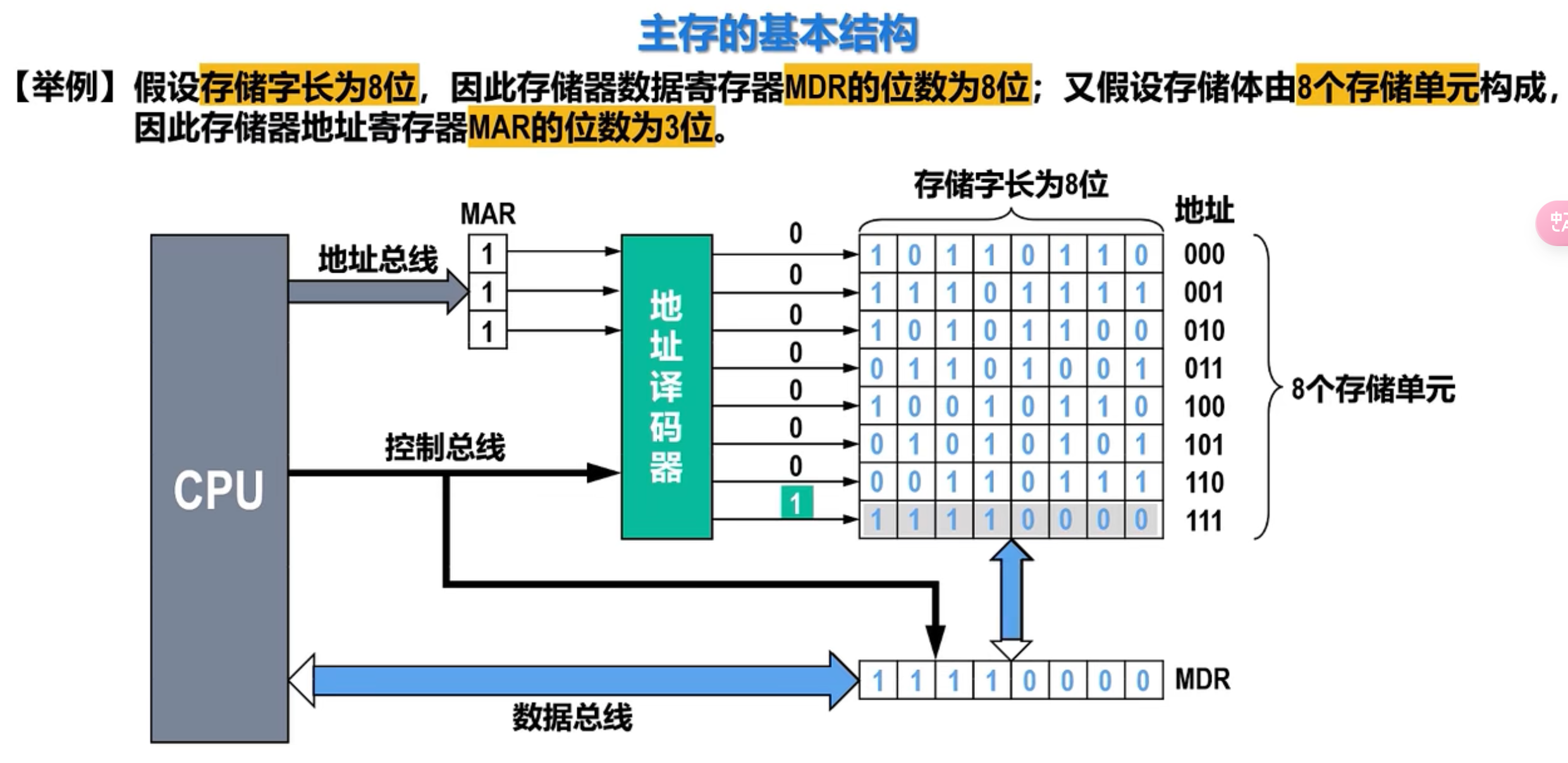

写入信息的过程,假设要写入 11110000 到 111 位置

- 首先数据总线把 11110000 传给 MDR

- 地址总线把 111 传给 MAR

- MAR 把 111 传给译码器选中第 7 个位置

- 修改第 7 个位置为 11110000

随着技术的发展,内存都被制成大规模电路芯片,MAR 和 MDR 都被集成到了 CPU 内部

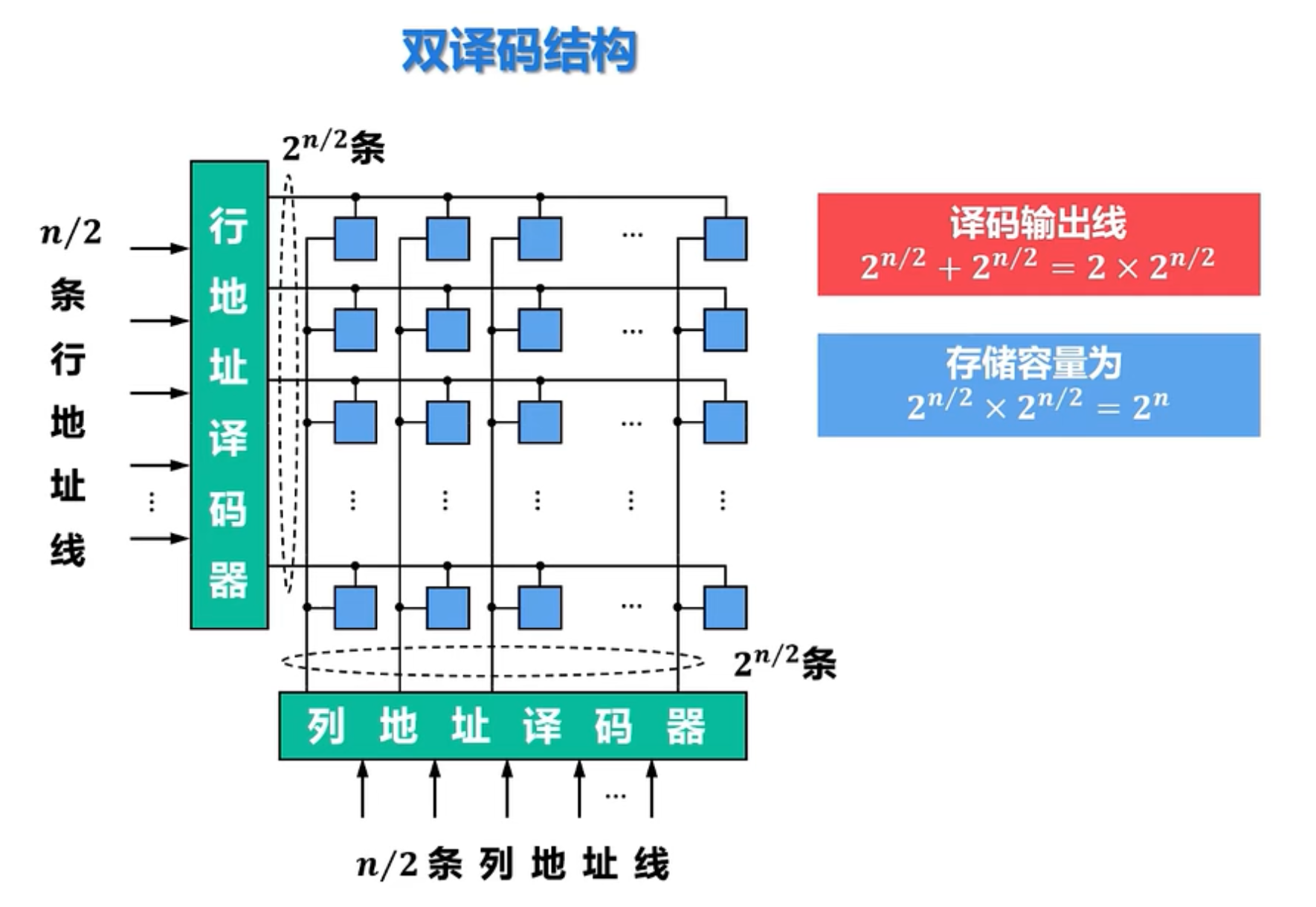

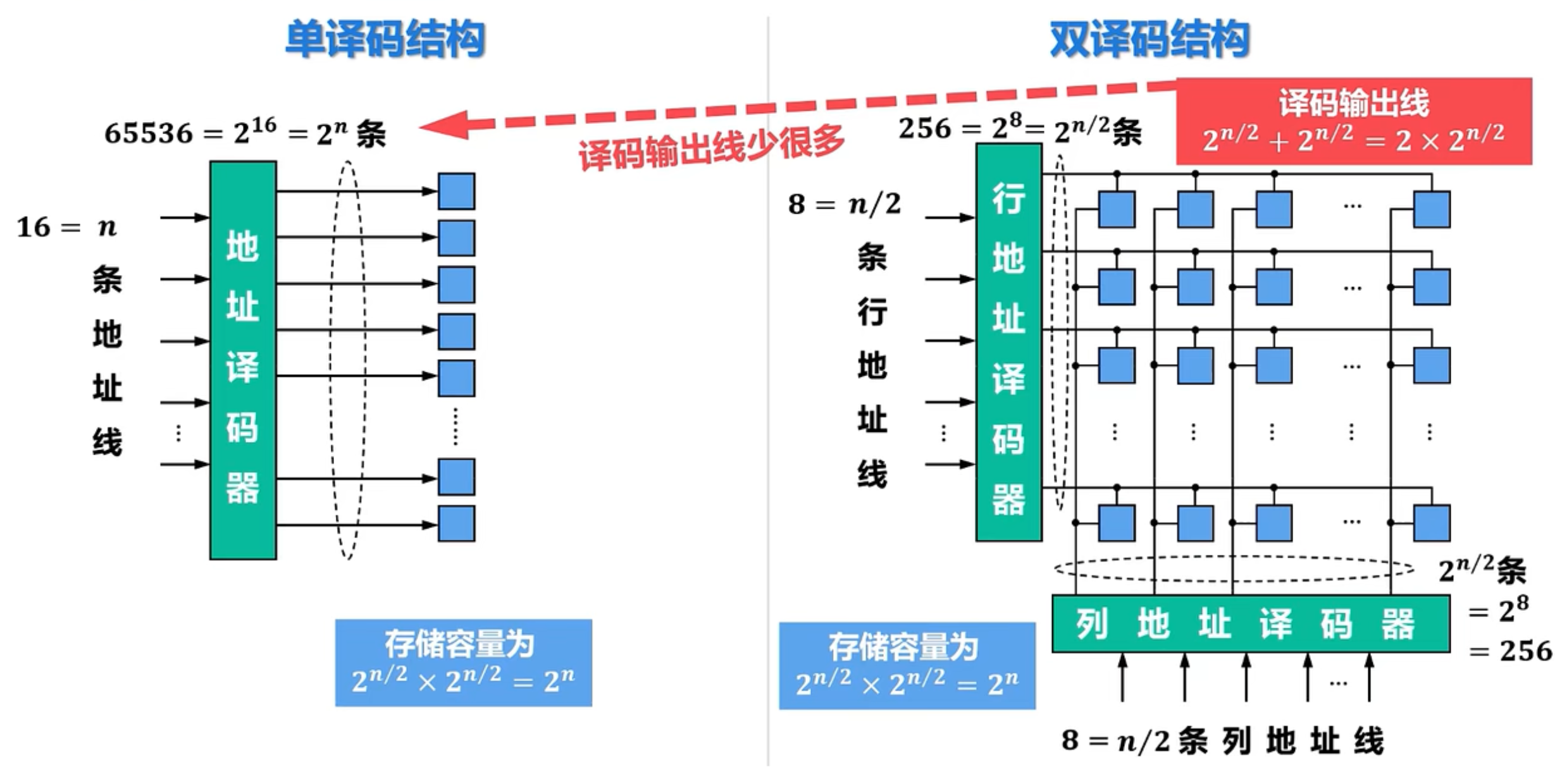

# 地址译码结构

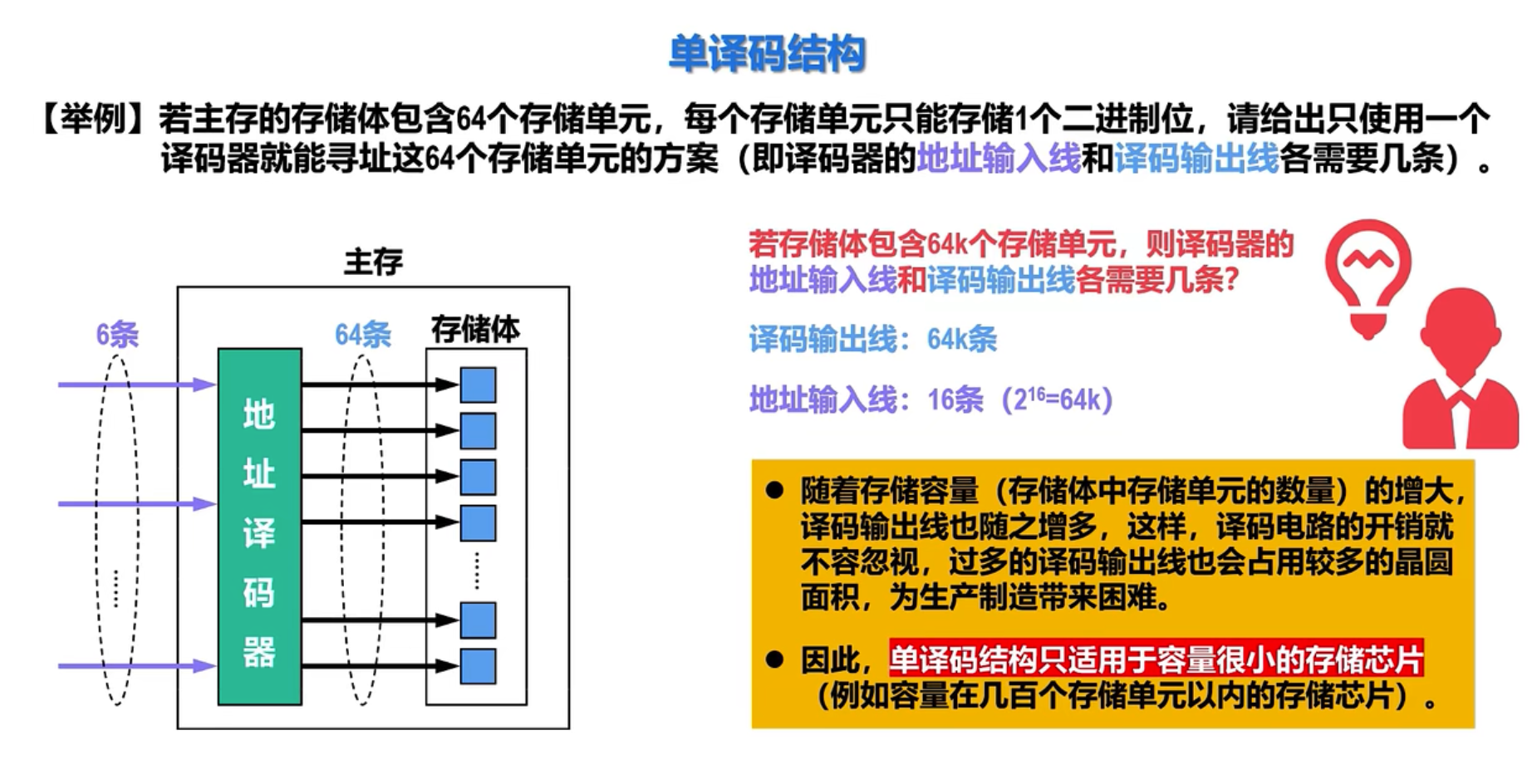

单译码结构

双译码结构

相对比之下,双译码结构的译码输出线减少很多

单译码结构只适用于容量很小的芯片,在大容量存储器中普遍采用双译码结构

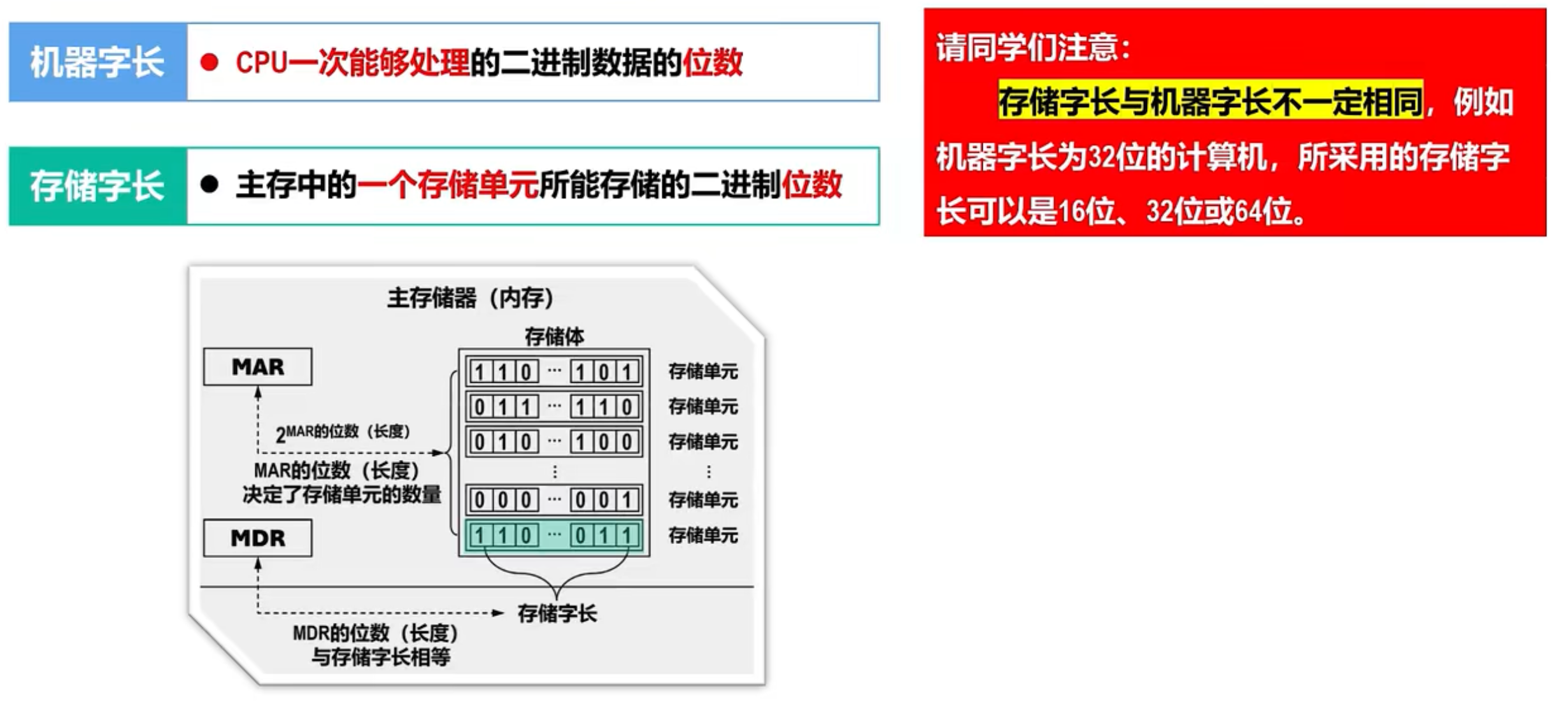

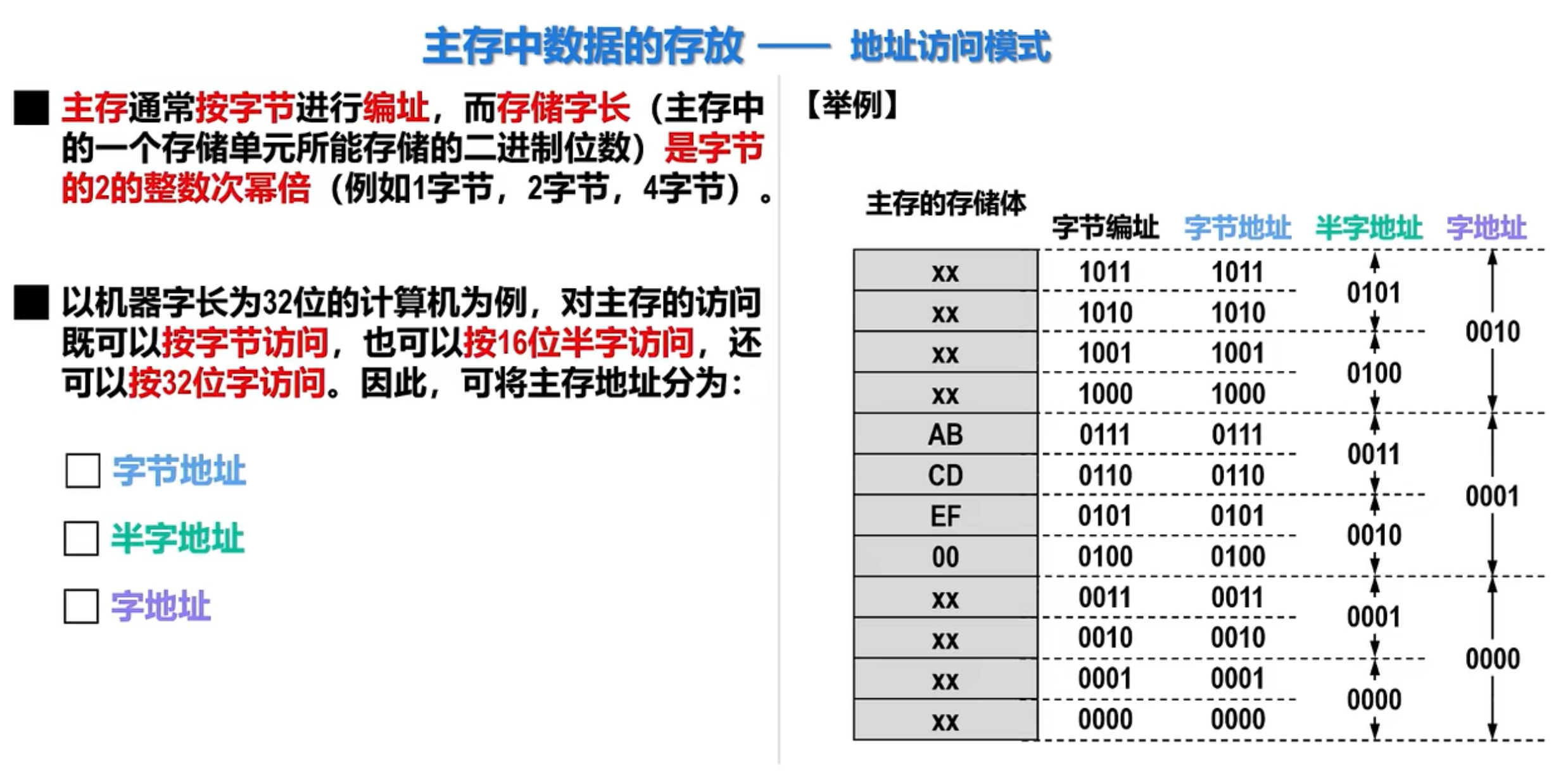

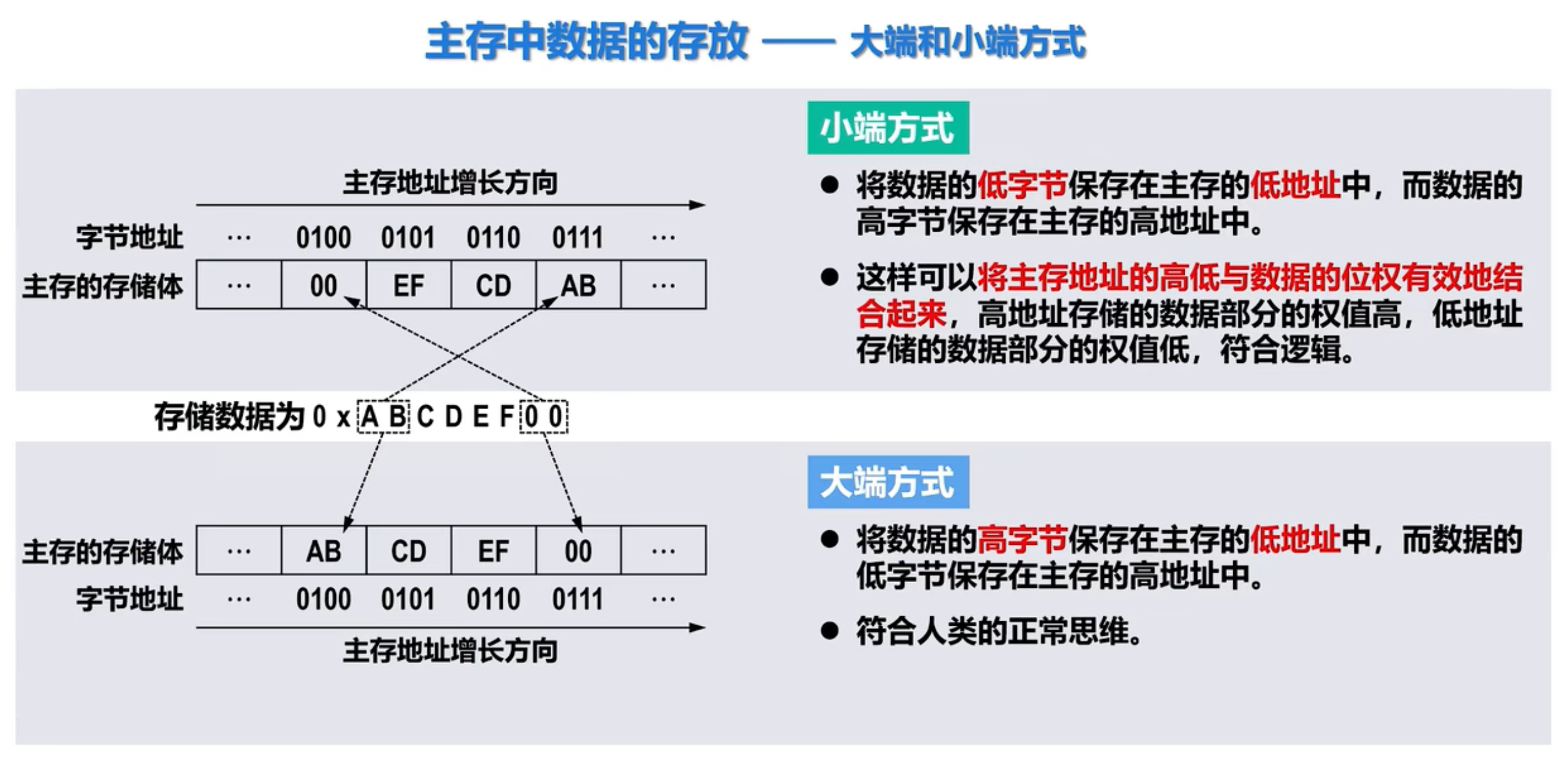

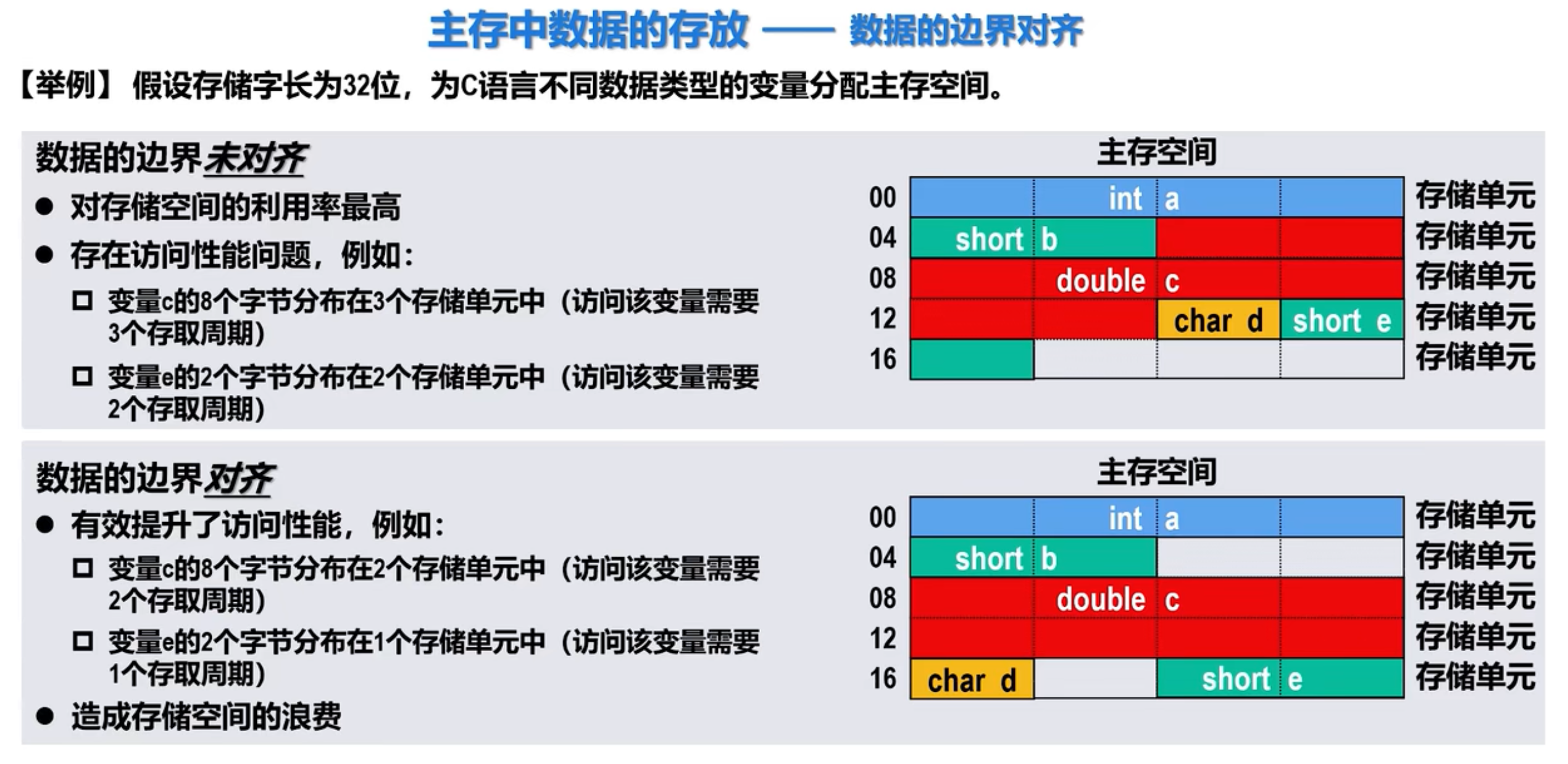

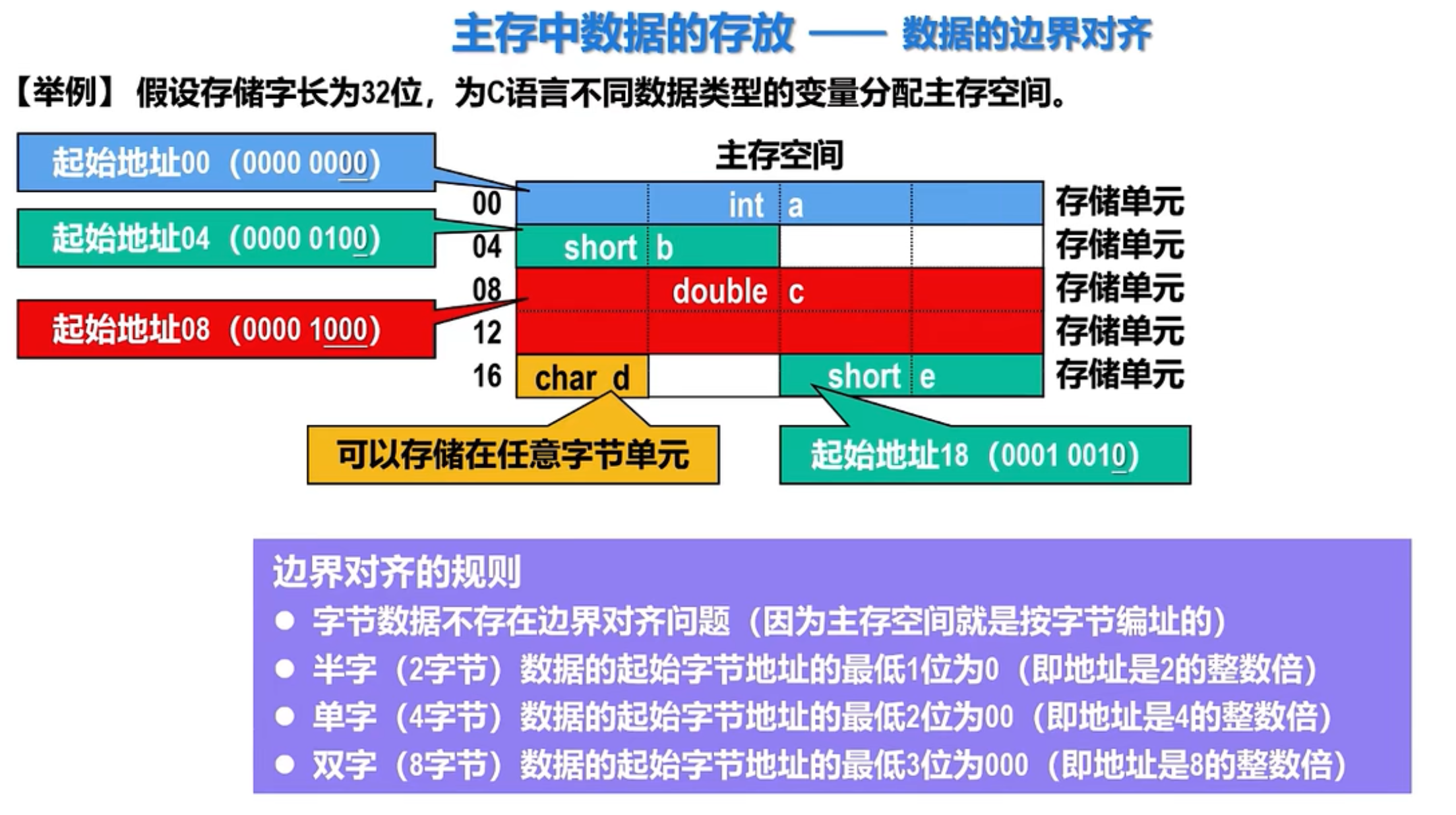

# 主存中数据的存放

- 存储字长:CPU 一次能处理的二进制数据的位数

- 存储字长:主存中的一个存储单元所能存储的二进制位数

字节地址右移一位得到半字地址,半字地址右移一位得到字

# 主存与 CPU 的链接

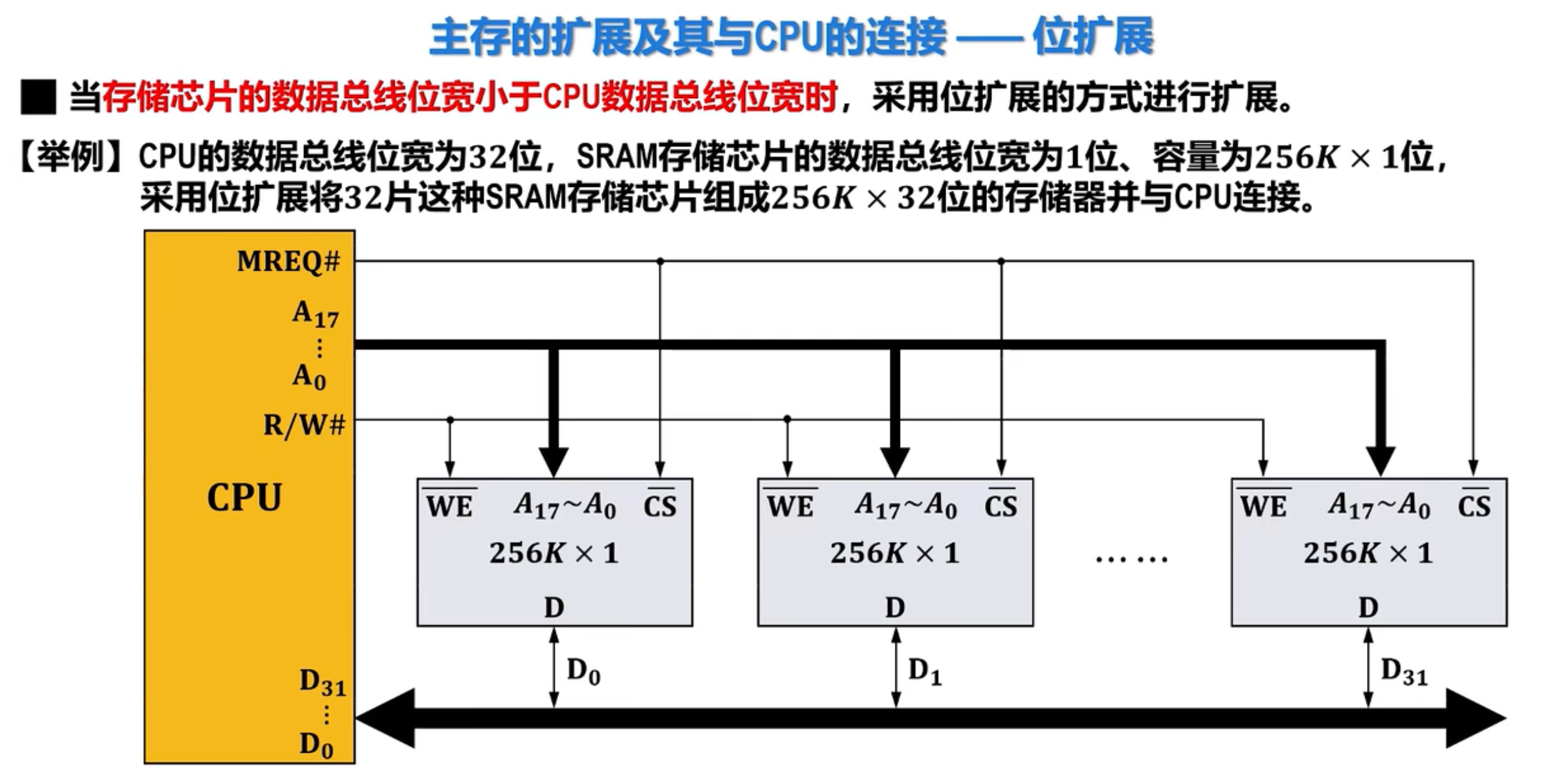

- 位拓展

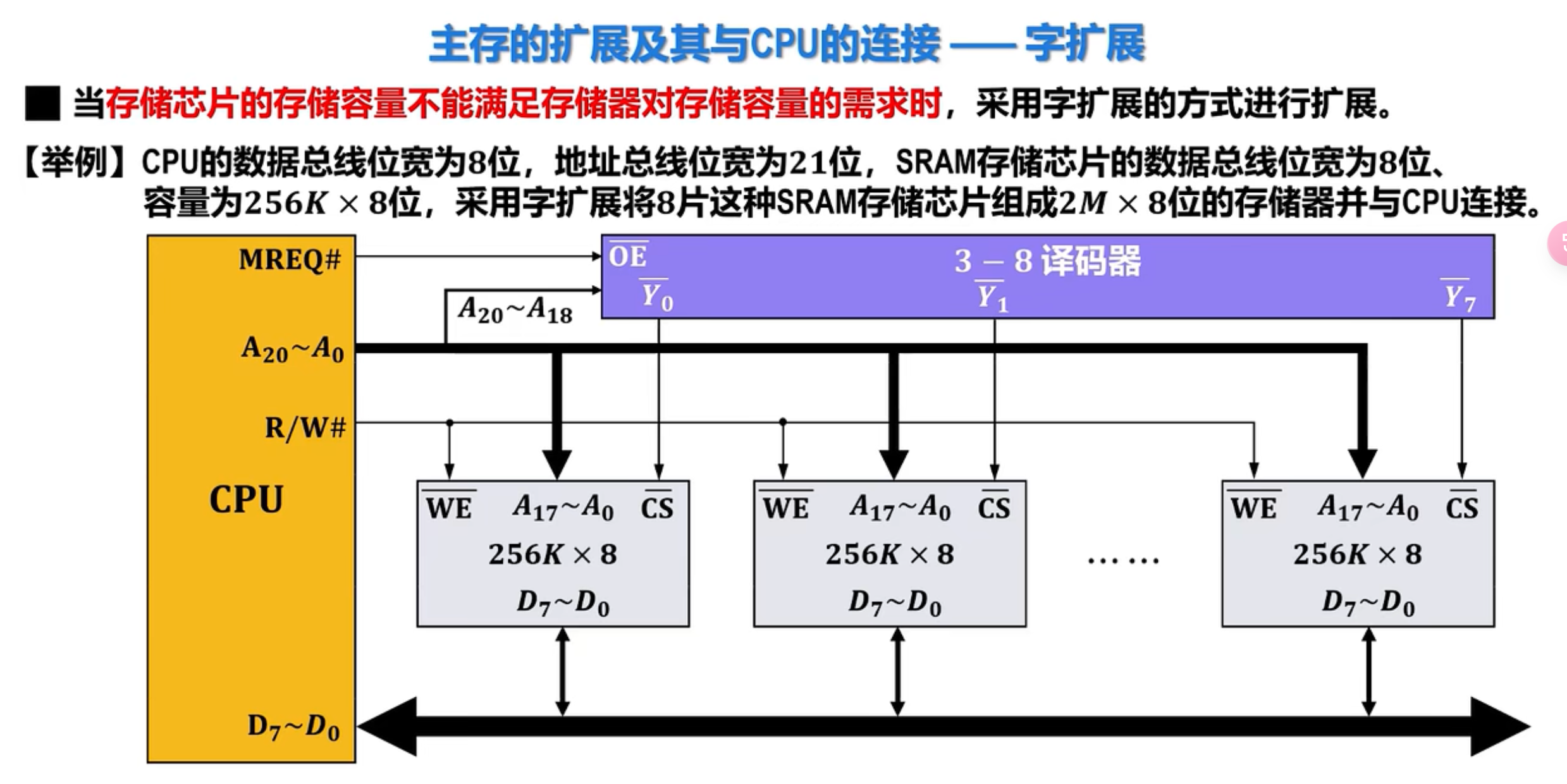

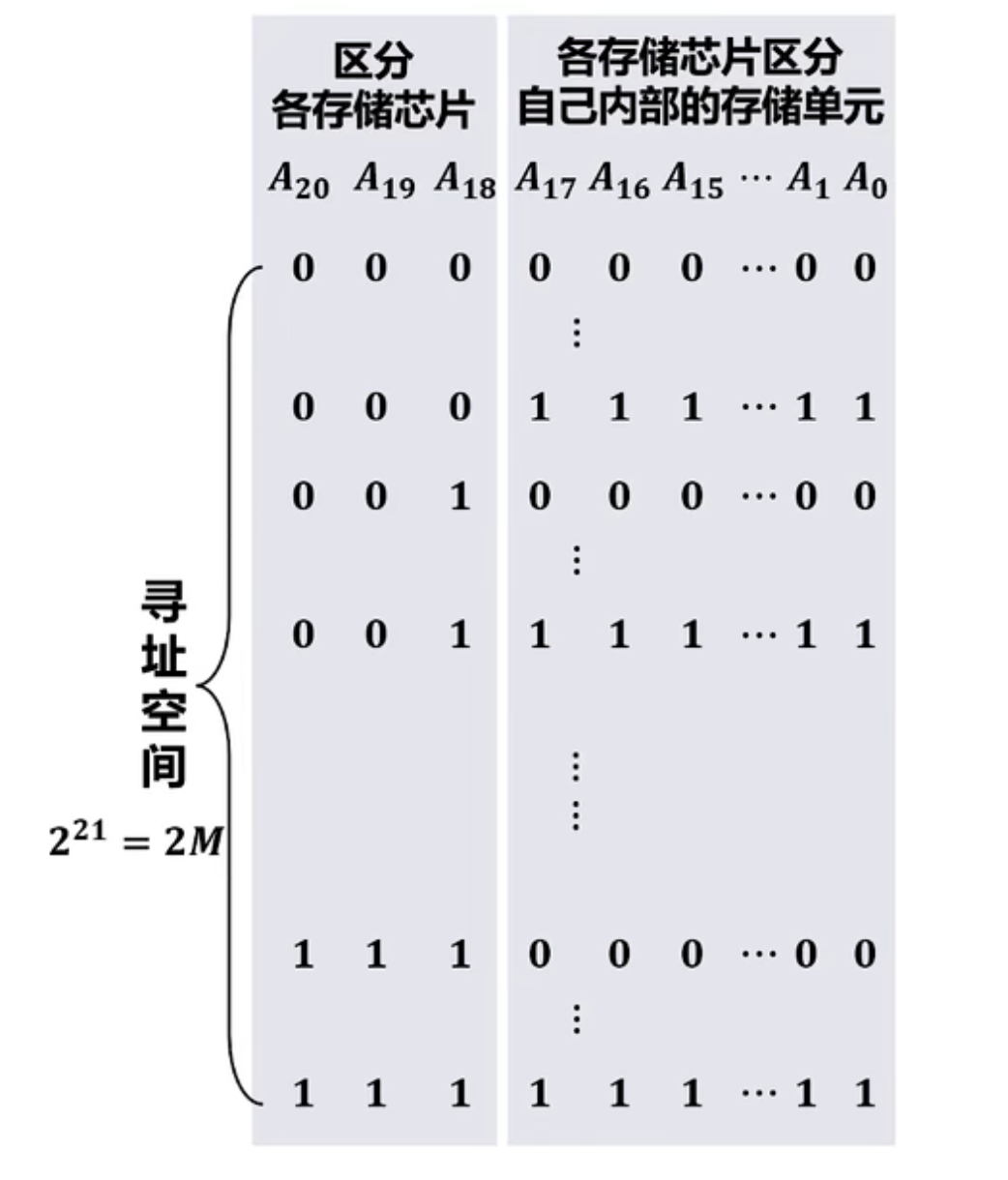

- 字扩展

可以理解为,CPU 数据总线的高三位用来判断要存储到哪一个 存储器,后面的位用来表示具体存到存储器的那个位置

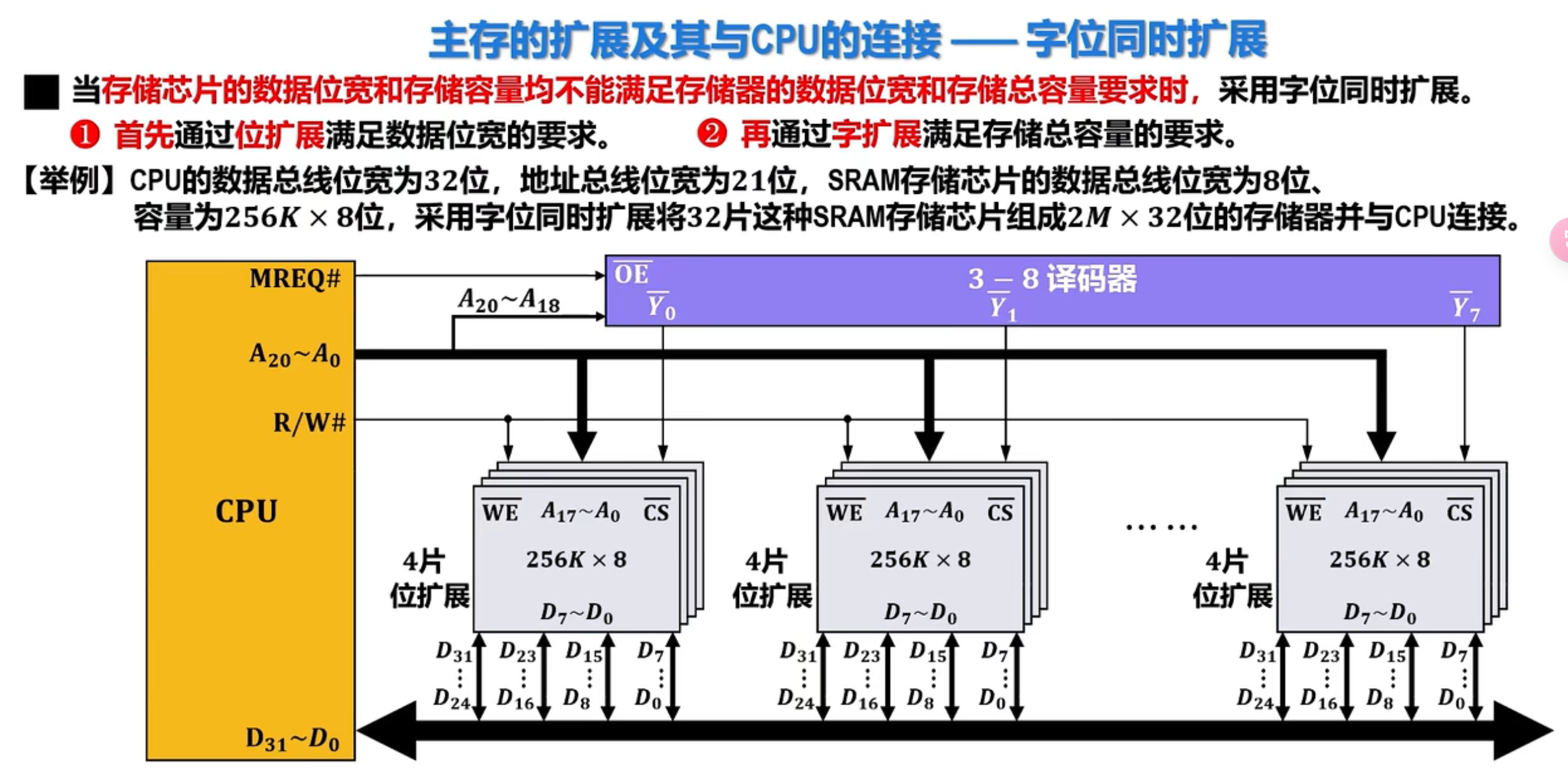

- 字位同时扩展

# 主存系统的优化

随着计算机技术的发展,主存的存取速度已经成为提升计算机系统性能的瓶颈

提升主存储器的存取速度的方法有:

- 使用高速原件来提高主存的访问速度

- 通过存储器的并行工作来提高主存的访问速度

- 双端口存储器

- 单体多字存储器

- 多体交叉存储器

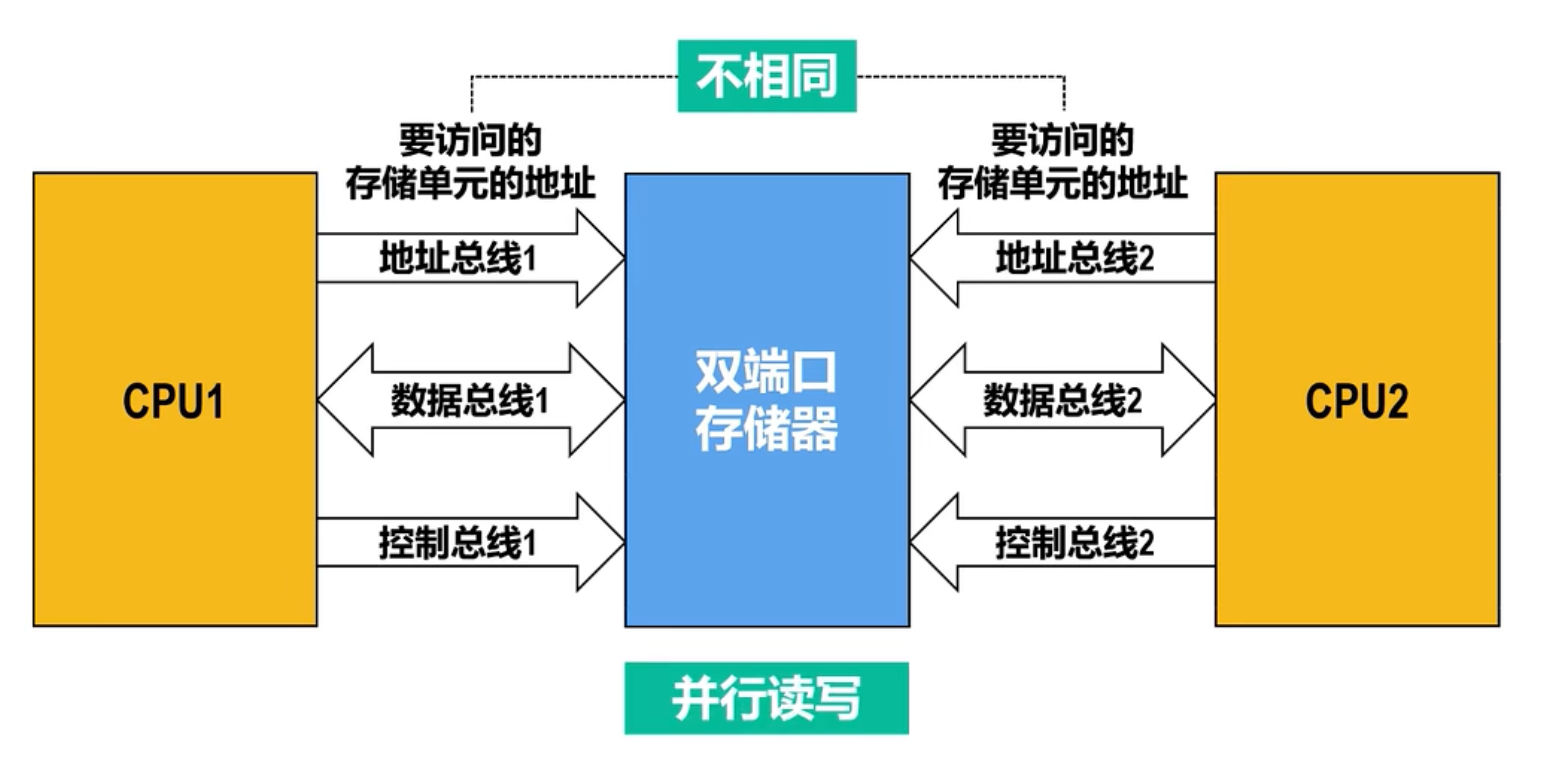

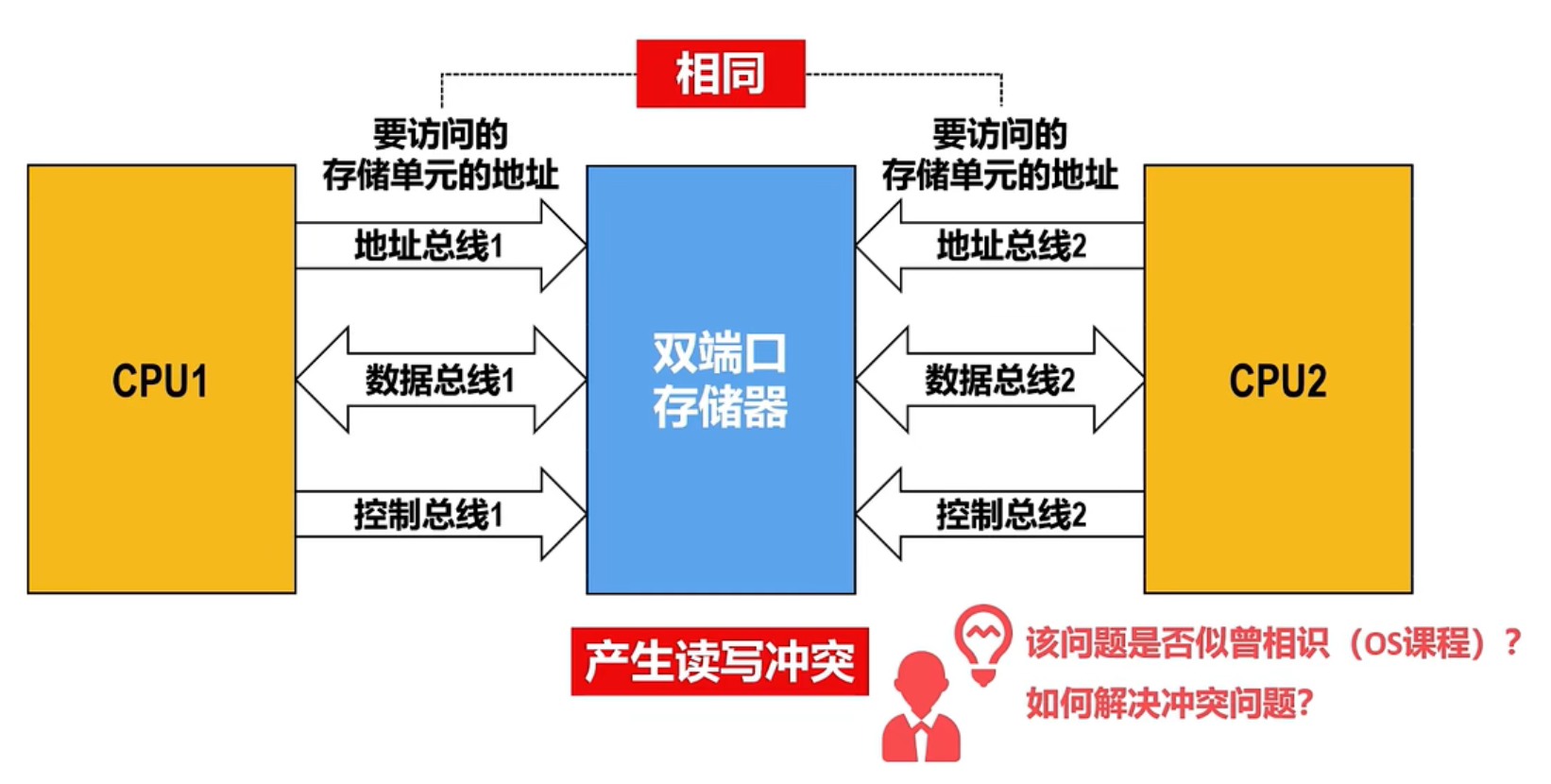

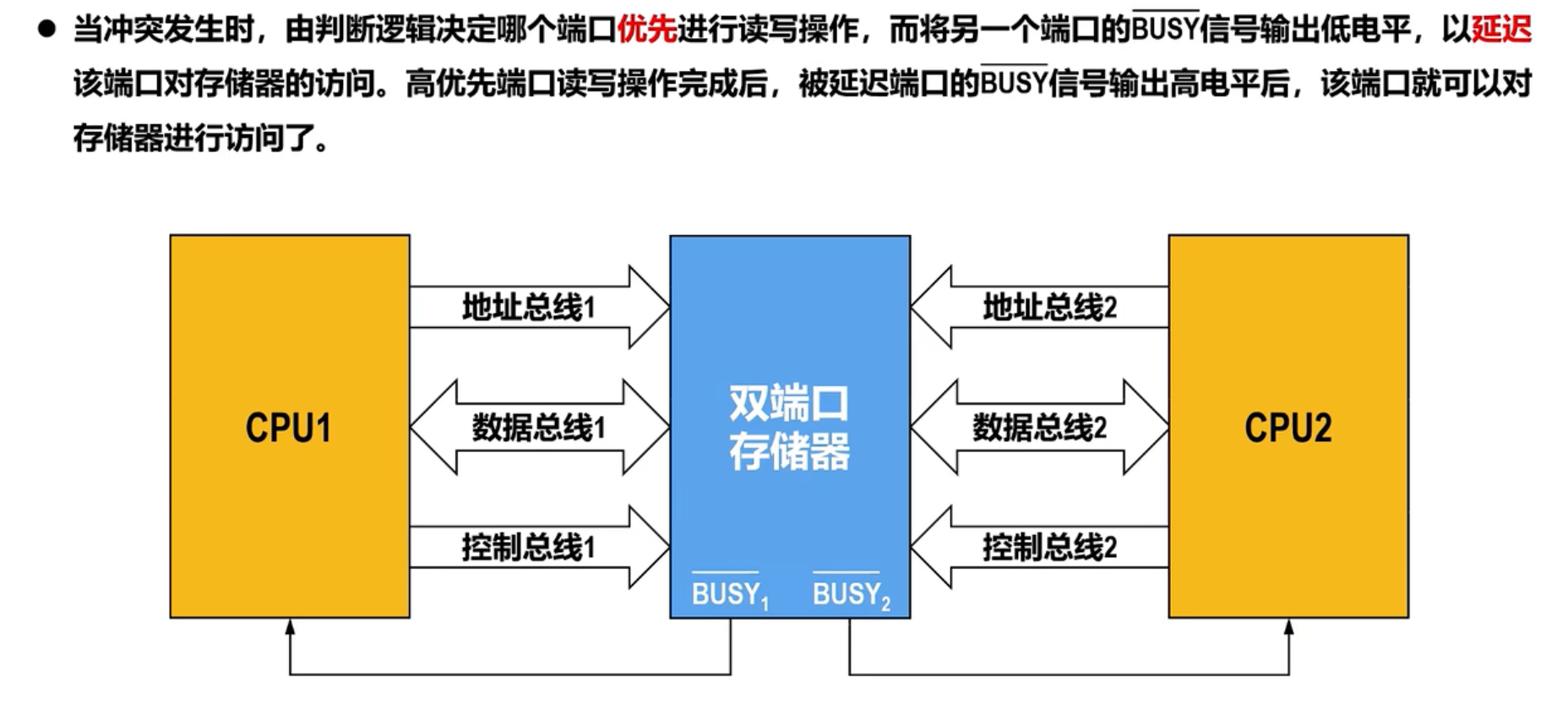

双端口存储器

双端口存储器有两套控制和地址总线

CPU 的两个核心访问不同的地址时,可以并行读写

当访问相同的地址时,就会产生读写冲突

使用一个忙标志判断是否有效

由于冲突时不可避免的,因此双端口存储器的访问速度不可能提高一倍

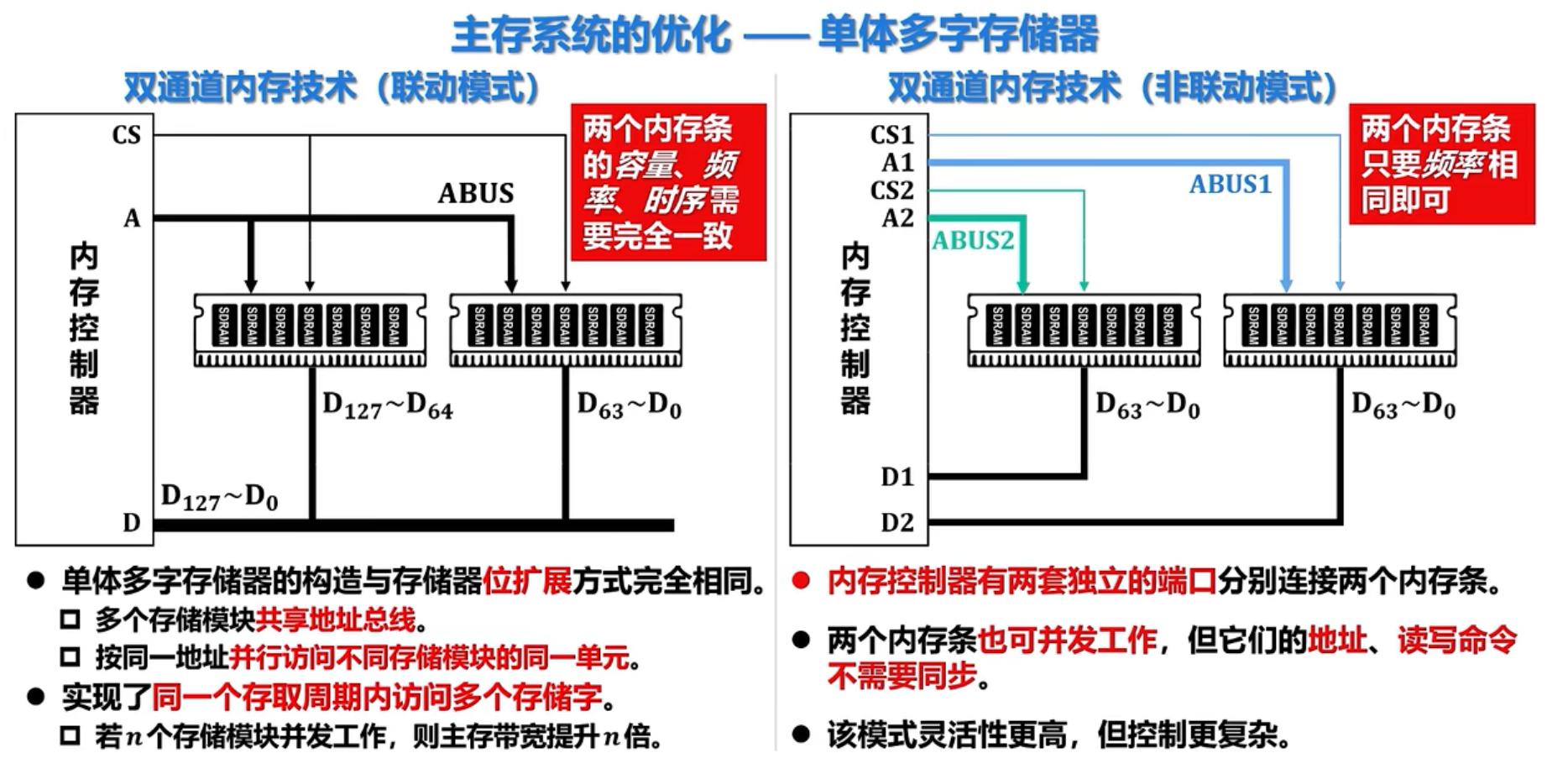

单体多字存储器

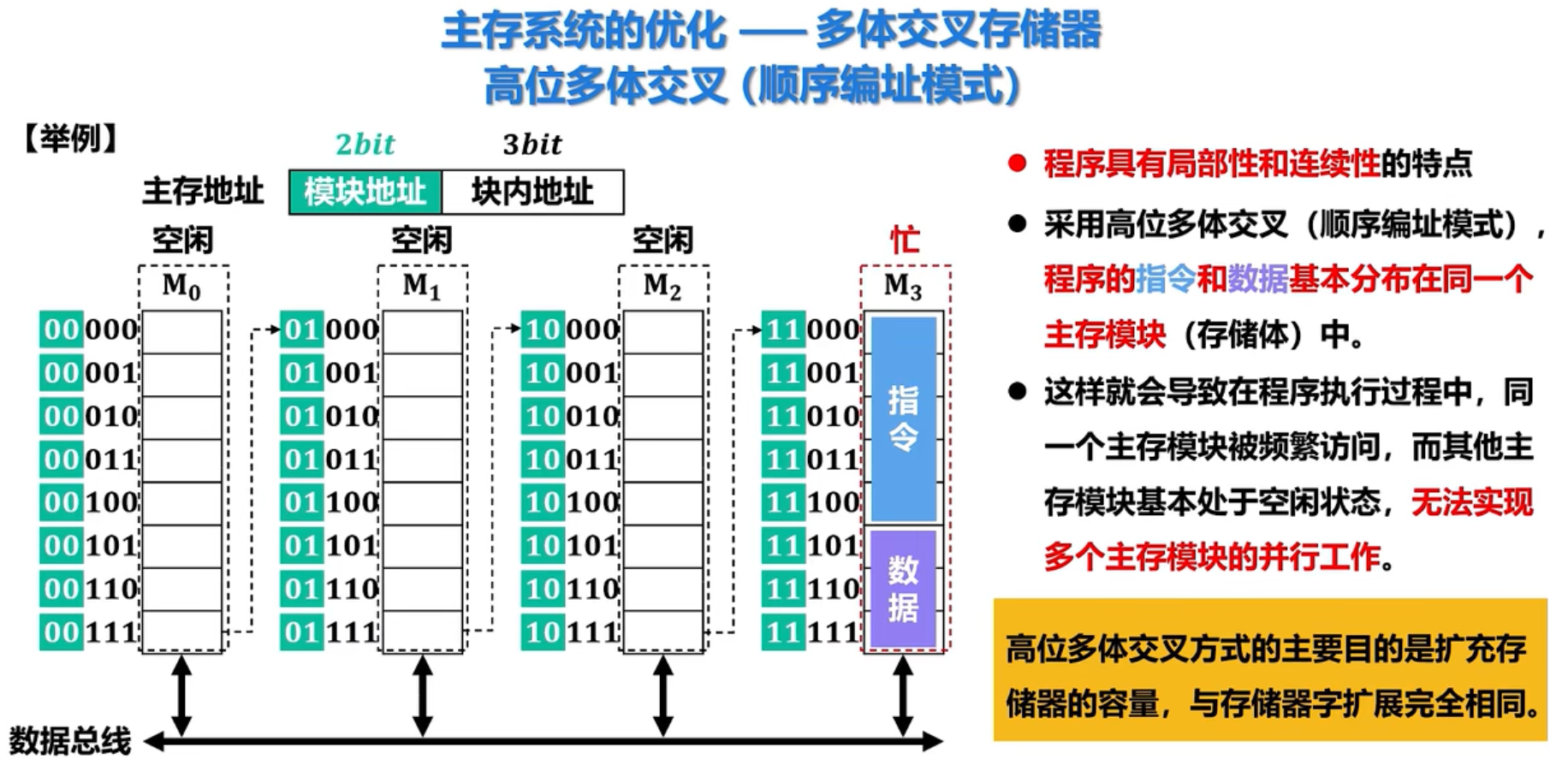

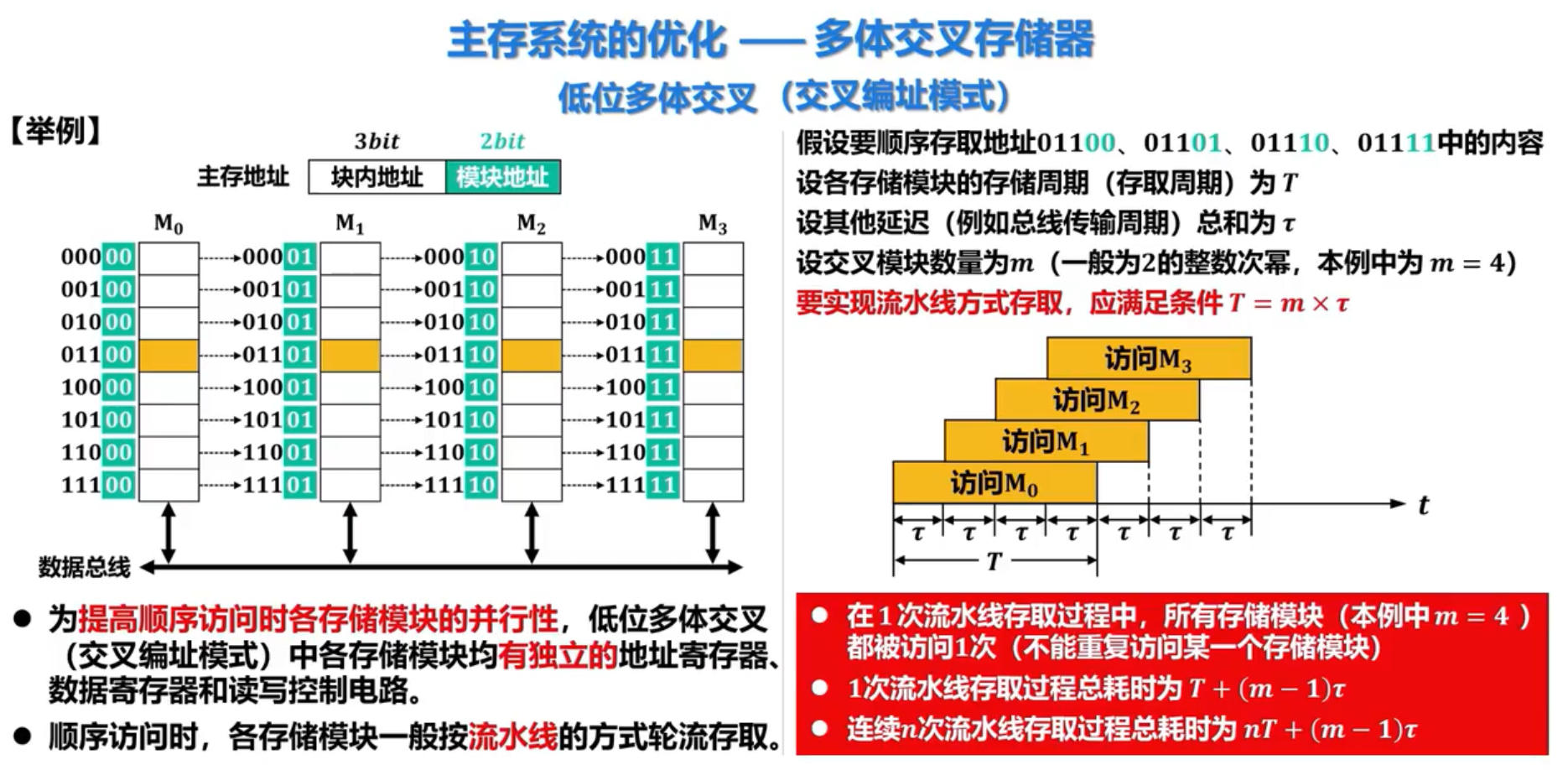

多体交叉存储器

根据多个存储器编制方式的不同,分为:高位多体交叉存储器,和低位多体交叉存储器

- 高位多体交叉

其实高位多体交叉存储器和字拓展完全相同

- 低位多体交叉

将高位多体交叉存储器的 模块地址 和 块内地址交换,即可得到低位多体交叉存储器

注意:可以从任意地址(某个模块,某个存储单元)开始顺序存取,不一定从 开始

# I/O 系统

# I/O 系统基本概念

- 外部设备:鼠标,键盘,打印机

- 接口:在各个外设与主机之间传输数据时进行各种协调工作的逻辑部件

- 输入设备:向计算机系统输入命令和文本、数据等信息的部件。键盘、鼠标

- 输出设备:计算机系统中的信息输出到计算机外部进行显示,交换的部件。显示器,打印机

- 外存设备:硬盘,光盘

# I/O 控制方式

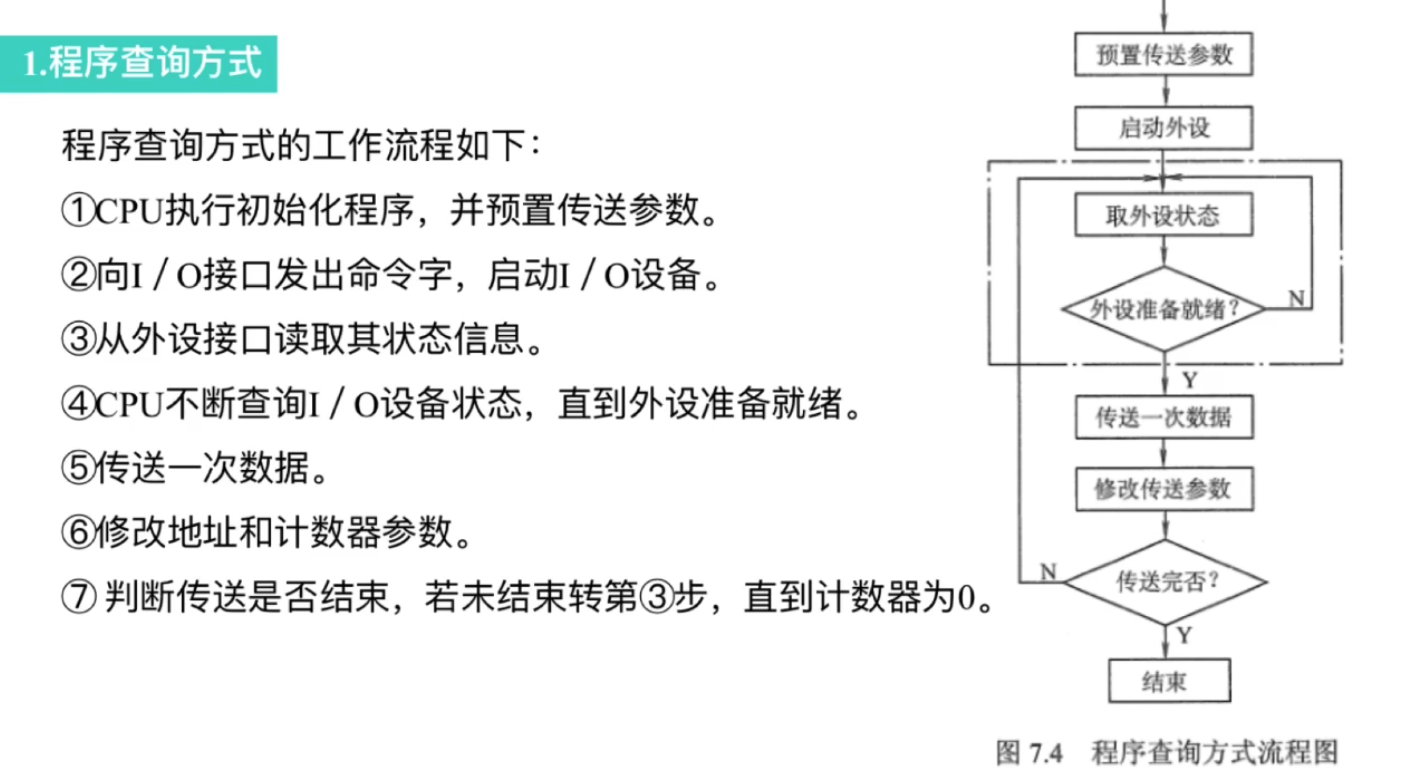

# 1. 程序查询方式

由 CPU 通过程序不断查询 I/O 设备是否已做好准备,从而控制 I/O 设备与主机交换信息

这个是有关一个设备的程序查询方式的流程图:

下面是程序中断方式的接口电路

# 2. 程序中断方式

计算机在执行程序的过程中,当出现异常或者特殊请求时,计算机停止现行程序的运行,转向对这些异常情况或特殊请求的处理,处理结束后再返回到现行程序的间断处,继续源程序,就是中断。

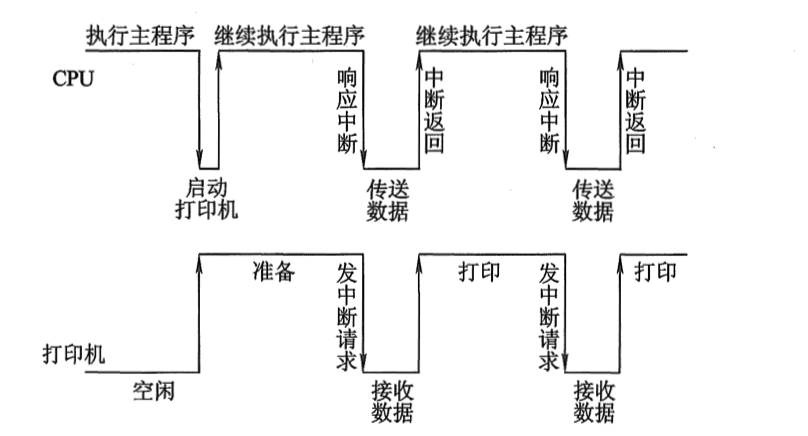

I/O 中断指的就是,设备准备的同时,CPU 不用等待,运行现有的程序,当设备准备就绪了并像 CPU 提出请求,中断 CPU 现行程序转入 I/O 服务程序,就叫 I/O 中断,如图:

只在 I/O 设备准备就绪并向 CPU 发出中断请求时才给予相应,在 I/O 设备的准备阶段或者工作阶段,CPU 都能去干自己的事情,能进一步提高 CPU 的工作效率

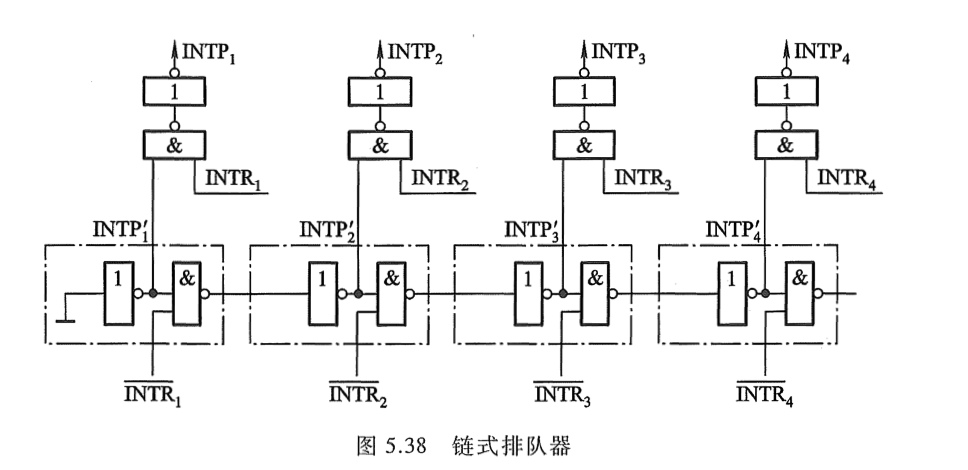

如果有多个 I/O 设备同时需要访问 CPU 呢?那么就需要比出 I/O 设备的优先级,可以通过软件或者硬件的方式比较优先级,但是硬件方式往往更快。下面就是一个硬件实现的排队器

例如,当 INTR1,2,3,4 同时发出请求时, 输出只会输出 INTR1 的请求。

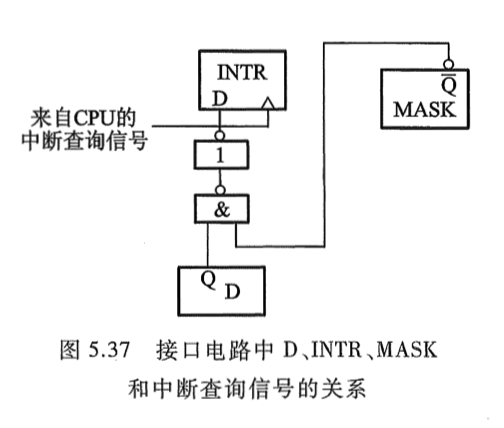

但是往往这样的优先顺序不是绝对的,我们就需要更加自由得确定 I/O 设备之间的优先级别,比如说,我们在运行第 4 个设备的时候,不想被设备 1 的请求打断。为了做到这一点,我们可以对每个设备单独设置一个触发屏蔽器 MASK,当运行第 个设备的时候,会设置所有设备的 MASK,若此时第 个设备的那一位 MASK 为 的话,就说明设备 被屏蔽了

从图中可以看出,当设备准备就绪(D = 1)且 设备未被屏蔽(MASK = 0) 的时候,向 CPU 提出中断请求信号(INTR = 1)

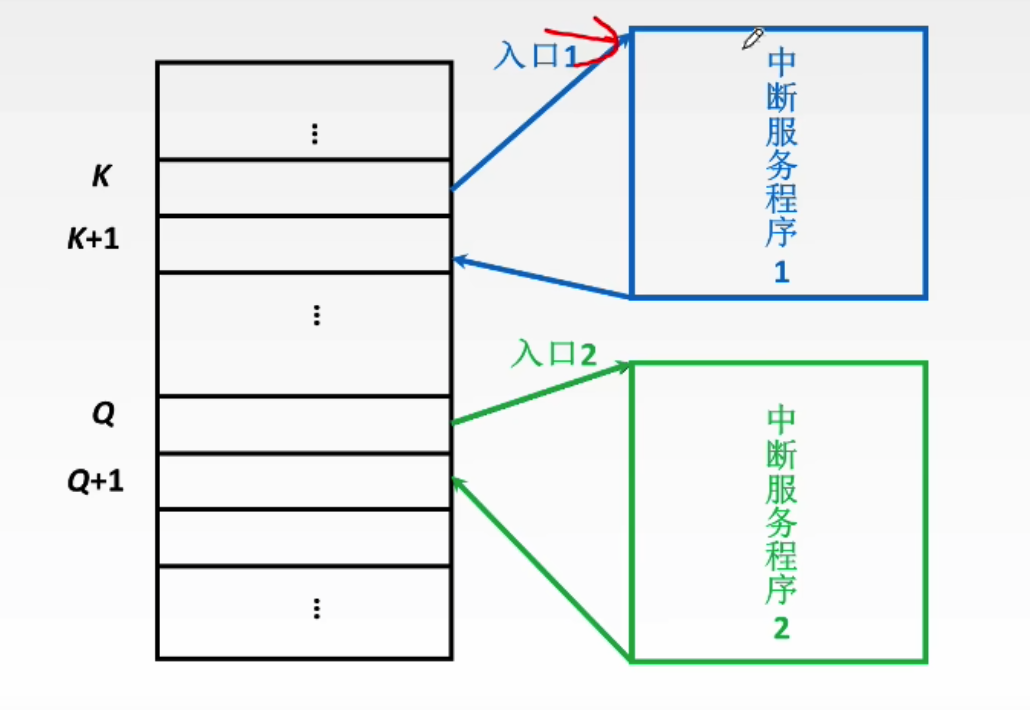

CPU 相应了中断之后,就需要转去执行设备中断服务程序,也就是这里的 PC 需要跳转到主存中设备中断服务程序的入口地址

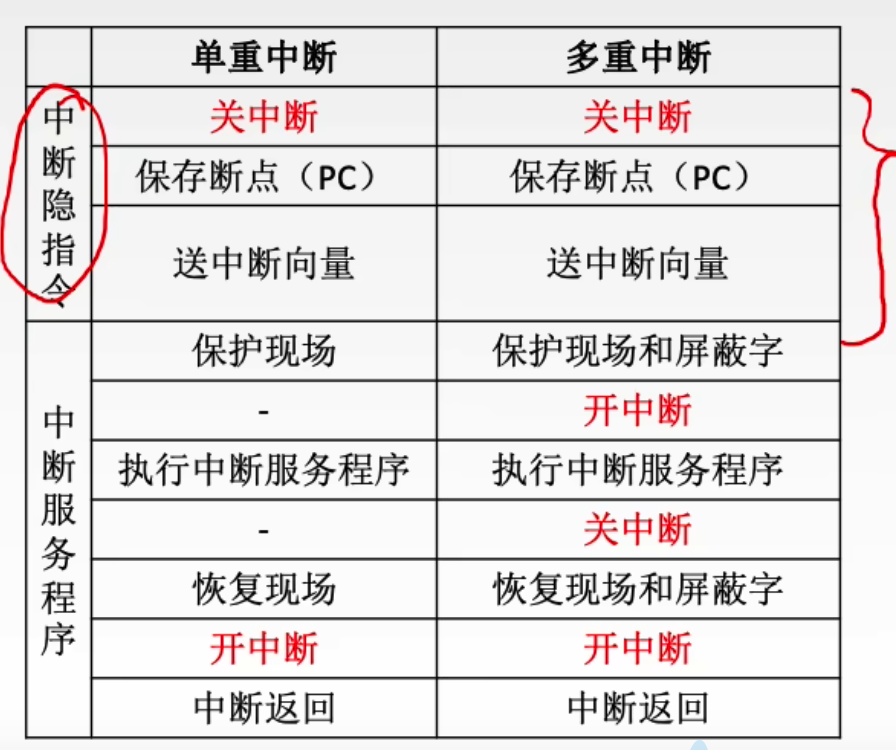

从 CPU 接收中断信号到开始运行中断服务程序这个过程中的一系列过程叫做中断隐指令,一般分为三步:

- 关中断:这个过程中不要被其他中断打断了

- 保存断点:记录 PC 当前的值 K

- 引入中断服务程序:就是把中断服务程序的入口地址传给 PC,这个地方其实设计了一个两级跳转的方式

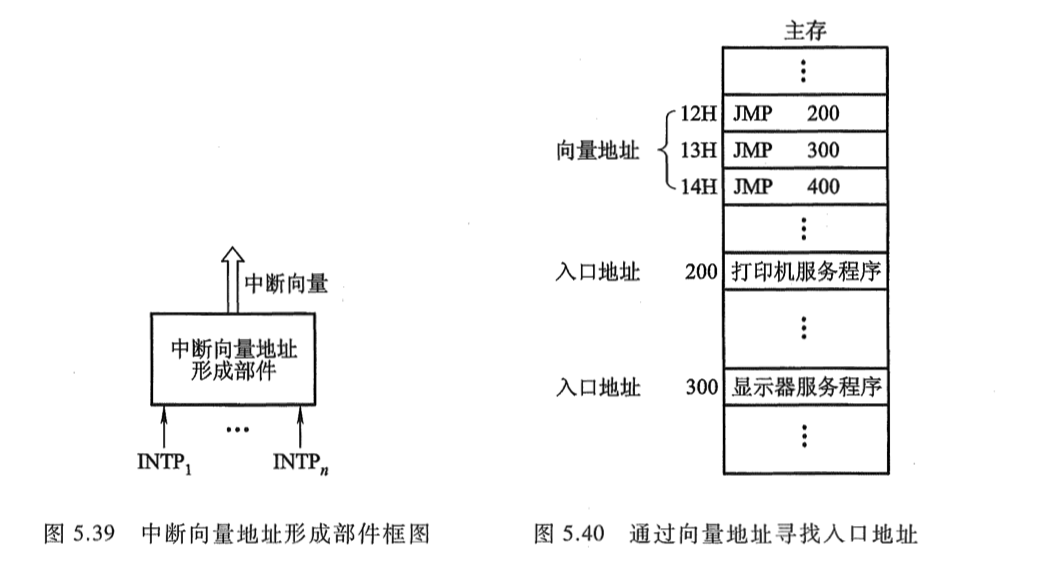

中断向量地址形成部件 将 中断向量的地址传给 PC,PC 先跳转到向量地址的地方,例如:12H,然后执行这个位置的 JMP 指令,跳转到入口地址,例如:200。

为什么要这样跳转两次?如果需要修改 打印机服务程序的值的时候,从现在的 200~299,改到 200~399,那么我们还需要去修改 硬件电路麻烦,但是现在这种方式只需要修改主存中的向量地址的后面的值就好了

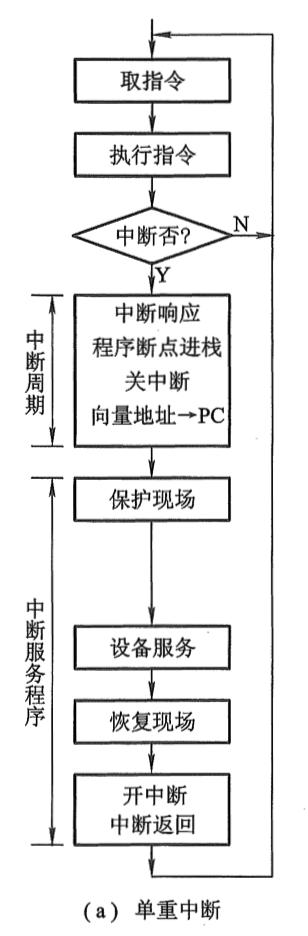

下面看一下完整的中断服务程序的流程:(中断周期可以理解为中断隐指令)

- 保护现场:保存程序的断点位置,和保留通用寄存器内容和状态寄存器中的内容,前者由中断隐指令完成,后者由中断服务程序完成。

- 中断服务:这是中断服务程序的主体部分,也是 CPU 和 I/O 设备交互的主要过程

- 恢复现场:将之前保护现场的内容恢复,可以用 pop 指令把寄存器中的一些值恢复

- 中断返回:让 PC 回到原来的断点处

实际上,在执行中断程序的时候是可以被更高界别的中断程序中断的(套娃)

只要在保护完现场之后,再开中断,恢复现场前关中断就好了

这个也叫多重中断

# 3. DMA 方式

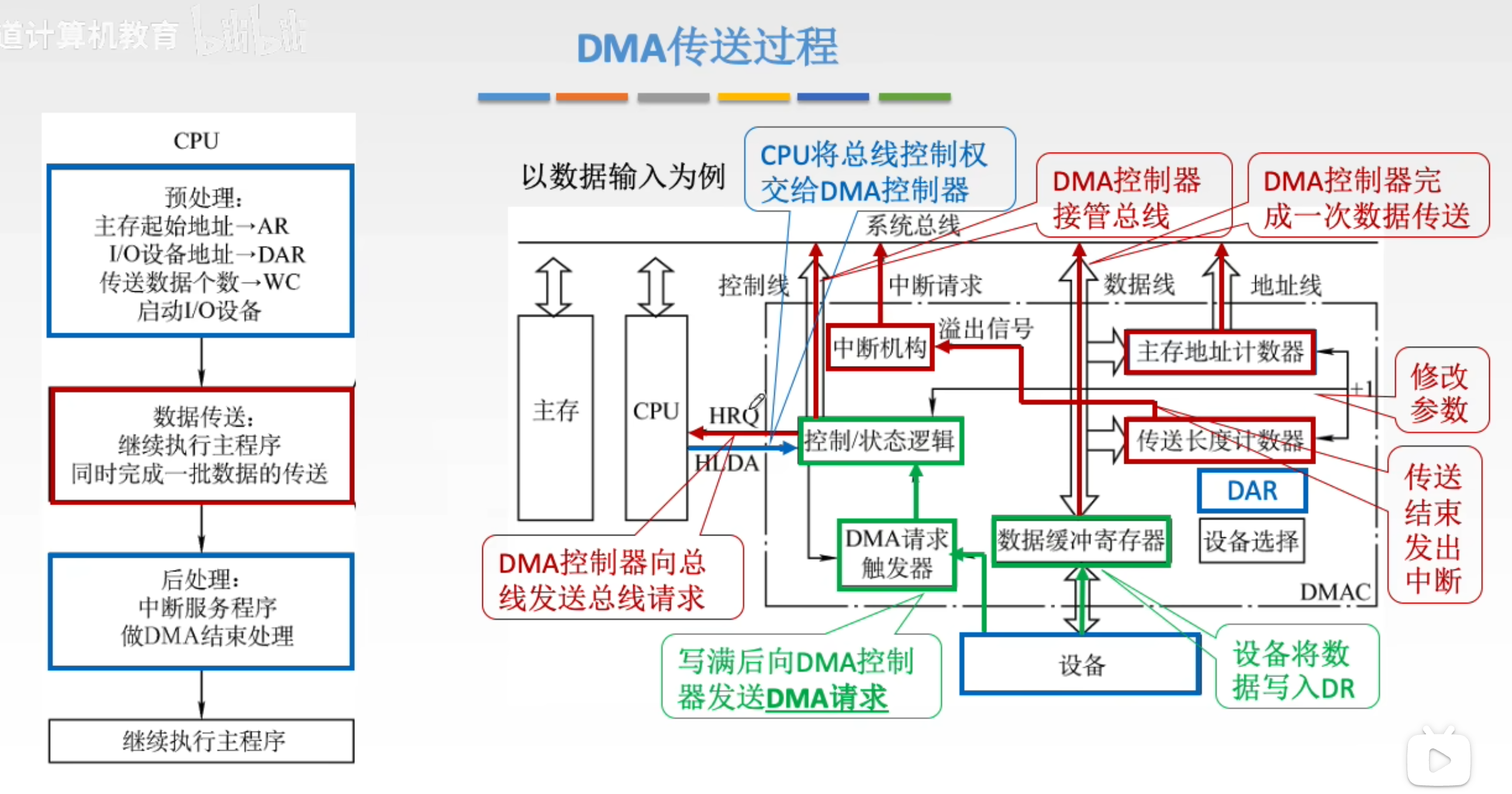

DMA 其实也可以理解为一个 I/O 设备接口,相当于 I/O 设备需要通过 DMA 和主存进行访问,DMA 一般用于处理块状的数据,或者比较高速的信息交换

DMA 和主存之间有一条单独的信息通路,所以能不通过 CPU 和主存交换数据。

图中就是 DMA 工作的一个基本过程:

- 预处理:

- CPU 给 DMA 表明是读数据还是写数据

- 给 DMA 的主存地址计数器(AR)写入初始地址

- 给 DMA 的 DAR 写入设备的读写地址

- 给 DMA 的 传送长度寄存器 WC 写入 传送数据的个数,表示需要传送多少个数据

- 数据传送

- 把一个字的数据冲到 数据缓冲寄存器 BR 中,

- DMA 通过 HRQ 申请总线控制权

- DMA 把数据缓冲寄存器打到主存中(输入为例)

- 修改主存地址计数器和传送长度计数器

- 后处理

- DMA 的中断机构向 CPU 提出中断请求,表示传送完毕

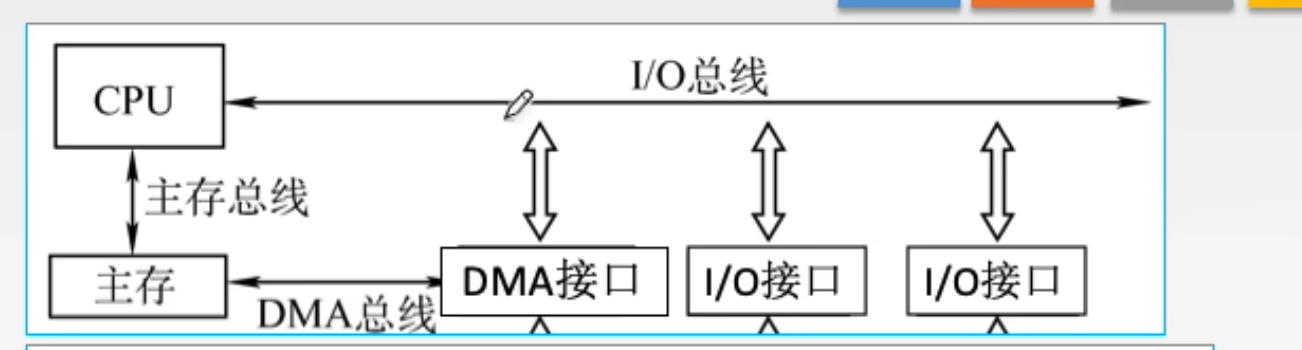

除了图中这种单总线的结构,DMA 还有一种三总线的结构

DMA 接口和主存之间能直接通信,但是如果 DMA 在访问主存的时候 CPU 也要访问主存,就会产生冲突,为了避免这种冲突,有三种解决方案

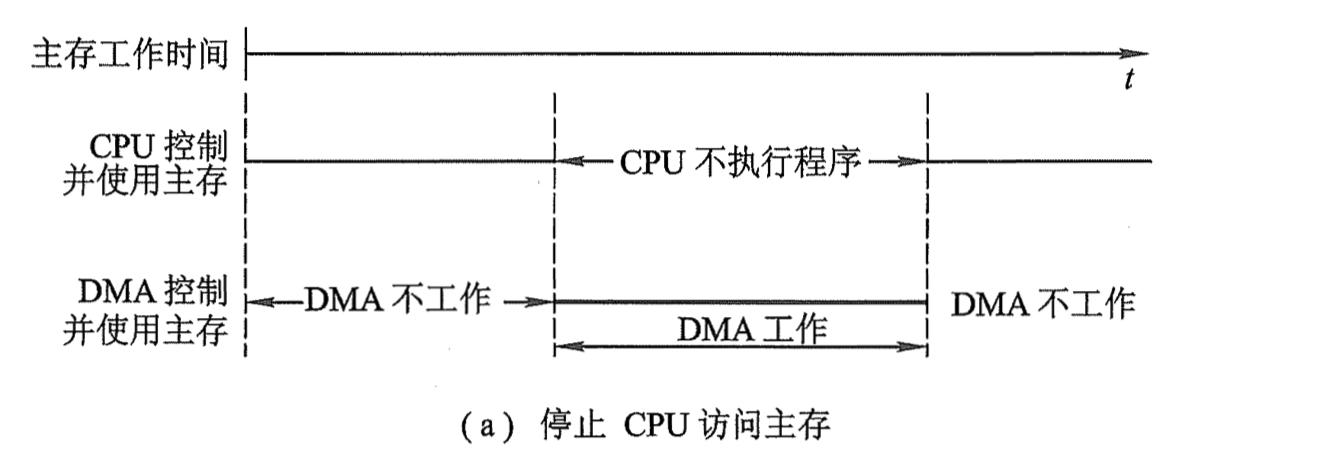

- 停止 CPU 访问主存

字面意思,就是等 DMA 访问完了之后 CPU 再访问

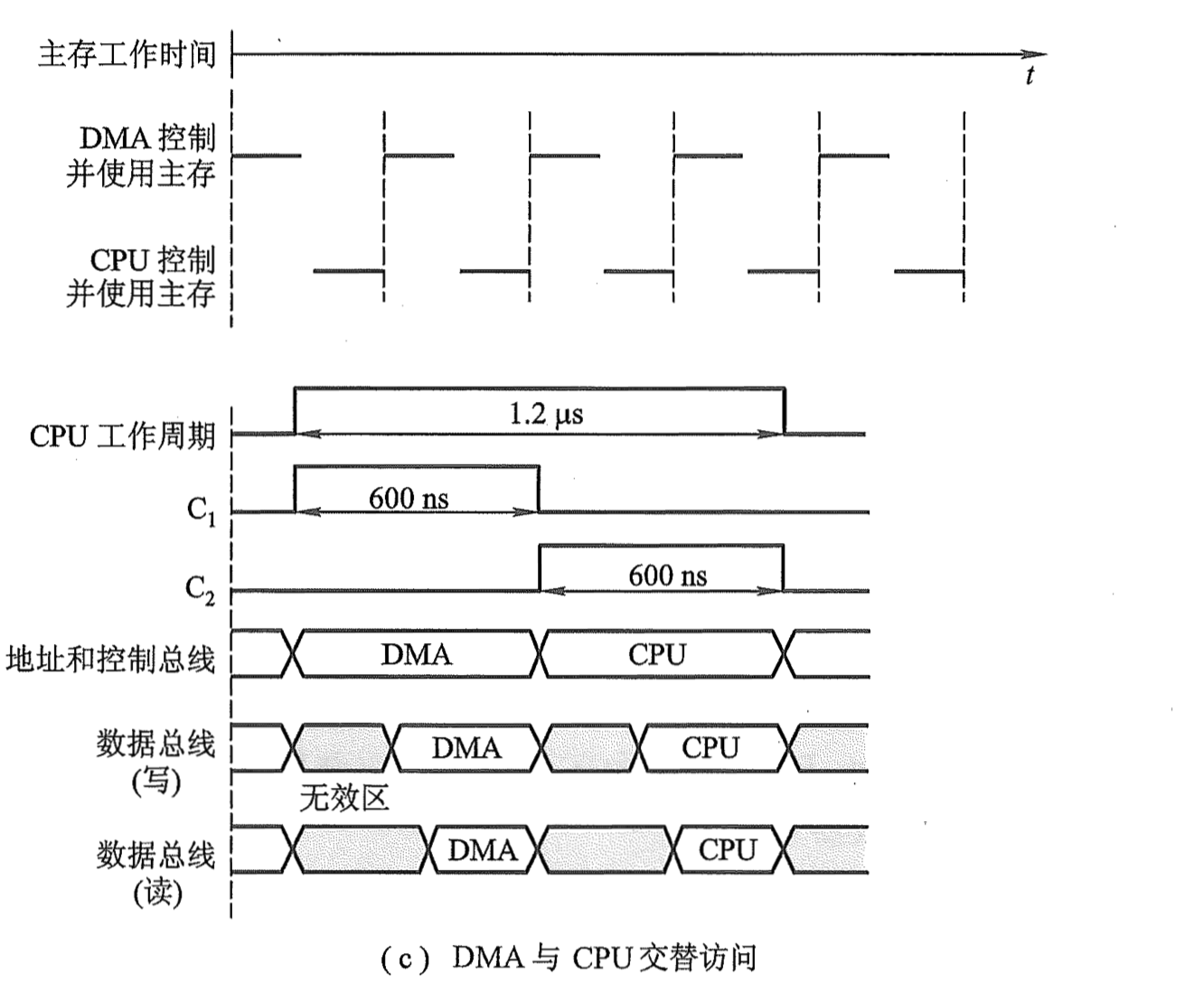

- DMA 和 CPU 交替访问

把 CPU 的工作周期的时间分两半,一半给 DMA,一半给 CPU,这种情况适用于 CPU 和 DMA 读写频率类似的情况,如果相差很大就会导致浪费

这种方式的硬件电路设计起来也很复杂

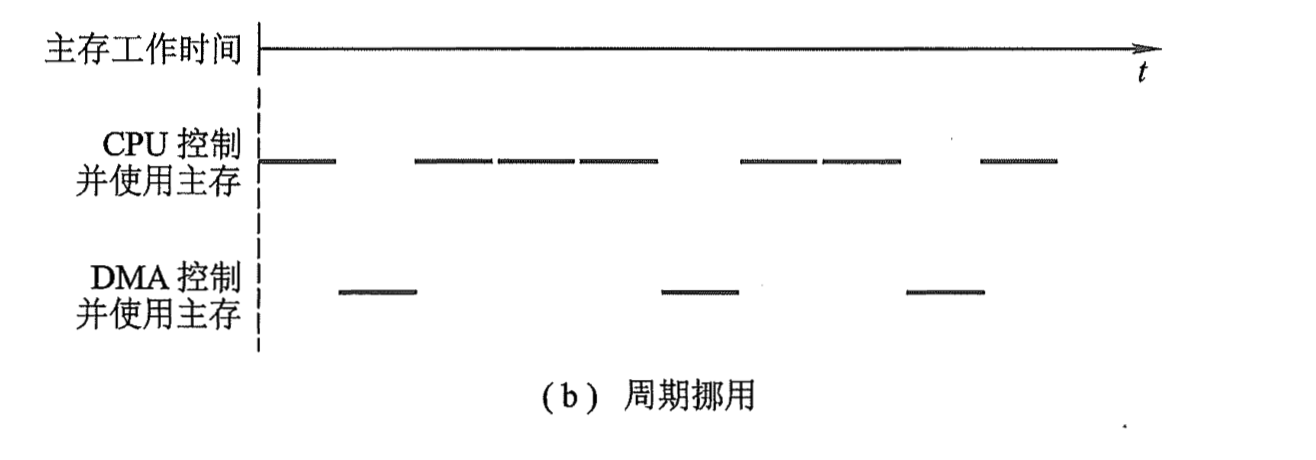

- 周期挪用(周期窃取)

当发出 DMA 请求时,I/O 设备挪用一个或几个主存周期给 DMA,而 DMA 不请求时, CPU 访问主存。当 DMA 发出访问请求时,CPU 可能的状态有三种:

- CPU 没有访问主存,在自己进行一些运算,这种情况直接挪用

- CPU 在访问主存,必须要等存取周期结束,CPU 将总线的占有权让出

- CPU 和 MDA 同时请求,这个时候 I/O 设备的访问优先级高于 CPU

周期挪用的方式是一种广泛采用的方法

# 4. 通道方式

在系统设于通道控制部件,每个通道都挂有若干外设,主机在执行 I/O 命令时,只需启动有关通道,通道将执行通道程序,从而完成 I/O 操作